# *LCD Module*

## *Product Specification*

: APPROVAL FOR SPECIFICATION

For Customer : \_\_\_\_\_  : APPROVAL FOR SAMPLE

Module No. : TSM1601A-01GC

For Customer's Acceptance :

| Approved by | Comment |

|-------------|---------|

|             |         |

Team Source Display :

| Presented by                                                                        | Reviewed by                                                                         | Organized by                                                                          |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

|  |  |  |

This module uses ROHS material

- 1 . REVISION RECORD

- 2. GENERAL SPECIFICATION**

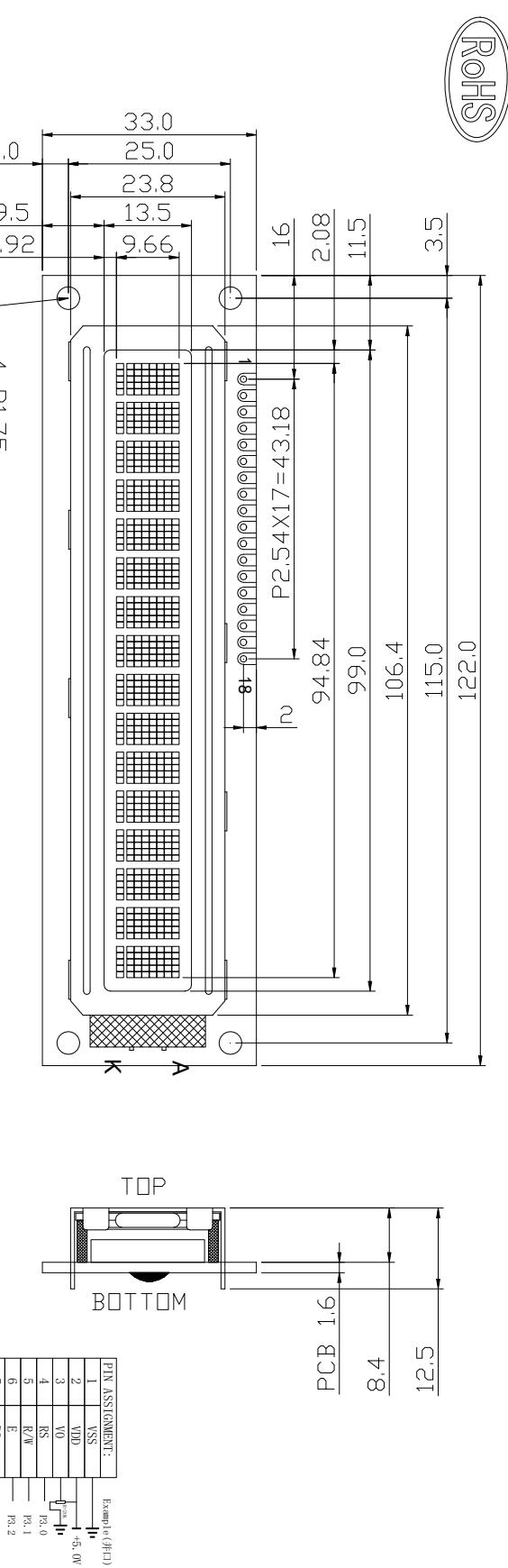

3. OUTLINE DEMENSION:

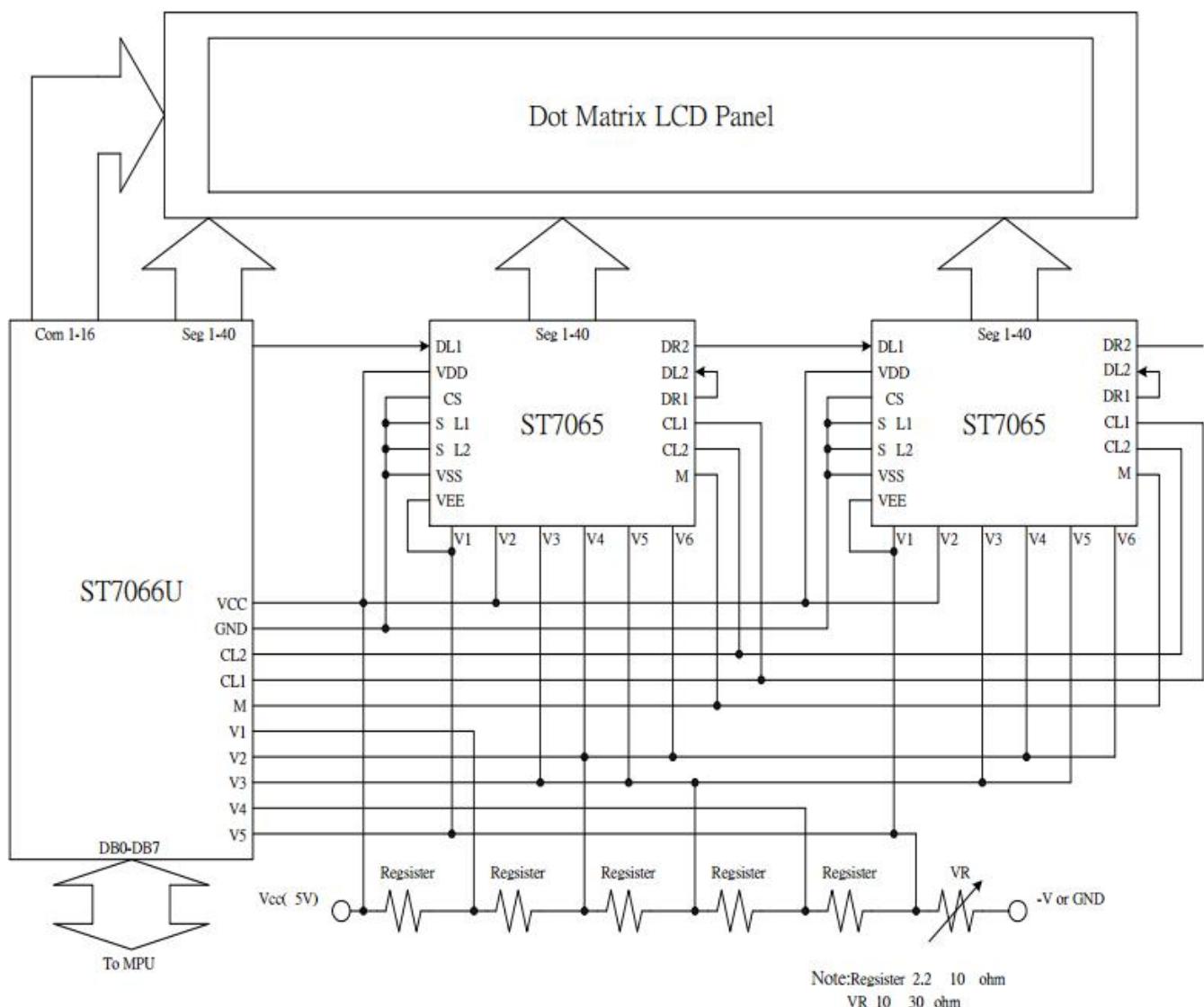

4. BLOCK DIAGRAM

5. ABSOLUTE MAXIMUM RATINGS

6. ELECTRICAL CHARACTERISTICS

7. ABSOLUTE MAXIMUM RATINGS FOR LED BACKLIGHT

8. PIN ASSIGNMENT

9. MPU INTERFACE

10. REFLECTOR OF SCREEN AND DISPLAY RAM

11. DISPLAY CONTROL INSTRUCTION

12. OPTICAL CHARACTERISTICS

13. POWER SUPPLY SCHEMATICS

14. APPLICATION EXAMPLE

- 15. PRECAUTION FOR USING LCM**

## 2.GENERAL SPECIFICATION

Interface with 4-bit or 8-bit MPU (directly connected M6800 serial MPU)

### Display Specification

Display Character: 16 character X 1 line      Character Font: 5X8 dots + cursor

Display color-Display background color : FSTN, RED-Green-Blue

Polarize mode: Positive, Transflective

Viewing angle: 6:00

Display duty: 1/16      Driving bias: 1/5

Character Generator ROM (CGROM): 8320 bits (192 characterX5X8 dots) &(32 characterX5X10 dots)

Character Generator RAM (CGRAM): 64X8 bits (8 charactersX5X8 dots)

Display Data RAM (DDRAM) : 16X8 bits (80 characters max)

### Mechanical characteristics (Unit: mm)

External dimension: 122.0X33.0X12.5

View area: 99.0X13.5      Character font: 5X8 dots + cursor

Character size: 4.84X9.66      Dots size: 0.92X1.1

Character pitch: 6.0X8.56

**Weight:**      **g**

POWER:      +5V

### **3. OUTLINE DEMENSION:**

| VER | DETIAL DISCRITION    | DATE       |

|-----|----------------------|------------|

| △   | The First Ammendment | 2017-03-25 |

客户确认签名/

Customer signature

|                                             |                             |            |      |

|---------------------------------------------|-----------------------------|------------|------|

| 1.DISPLAY TYPE:                             | FSTN/TRANSFLECTIVE/POSITIVE |            |      |

| 2.VIEWING DIRECTION:                        | 6:00                        |            |      |

| 3:BLACKLIGHT COLOR:                         | VF=5.0V IF <45mA RGB        |            |      |

| 4.DRIVER IC:                                | ST7066                      |            |      |

| 5,OPERATING TEMP:                           | -20°C~+70°C                 |            |      |

| 6,STORAGE TEMP:                             | -30°C~+80°C                 |            |      |

| 7,Drive Method:                             | 1/16DUTY                    | 1/5        | BIAS |

| 8,OPERATING VOLTAGE:                        | VDD=5.0V                    | ,VLCD=4.7V |      |

| 9,CONNECTOR:                                | ZEBRA                       |            |      |

| 10,UNMARKED TOLERANCES:                     | ±0.3mm                      |            |      |

| 11,REQUIREMENT ON ENVIRONMENTAL PROTECTION: | ROHS                        |            |      |

Circuit Diagram

color: RGB

DETAIL SCALE:2:1

15 LED-A

16 LED-MR

17 LED-MG

18 LED-RB

5V +5.0V

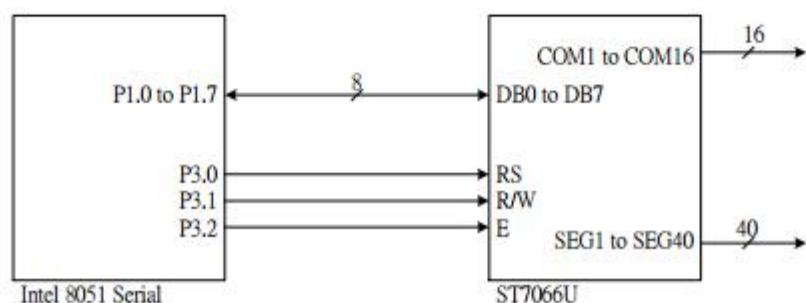

#### 4. BLOCK DIAGRAM:

#### 5. Absolute Maximum Ratings

| Characteristics       | Symbol    | Value                         |

|-----------------------|-----------|-------------------------------|

| Power Supply Voltage  | $V_{CC}$  | -0.3 to +7.0                  |

| LCD Driver Voltage    | $V_{LCD}$ | $V_{CC}-10.0$ to $V_{CC}+0.3$ |

| Input Voltage         | $V_{IN}$  | -0.3 to $V_{CC}+0.3$          |

| Operating Temperature | $T_A$     | -30°C to + 80°C               |

| Storage Temperature   | $T_{STO}$ | -55°C to + 125°C              |

## 6.ELECTRICAL SPECIFICATIONS(Ta=25°C, Vdd=5.0V)

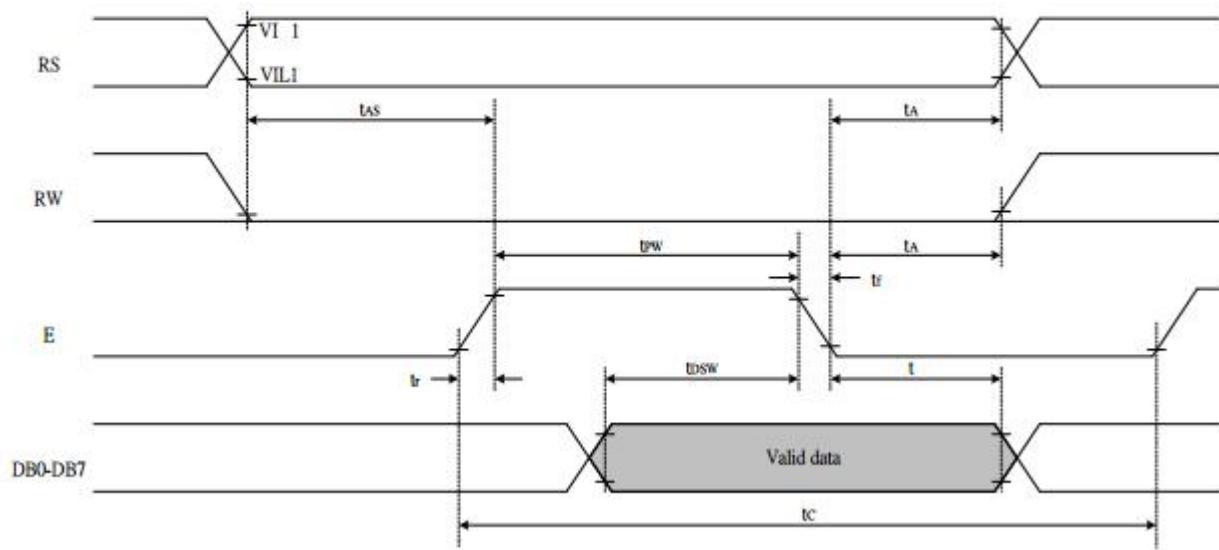

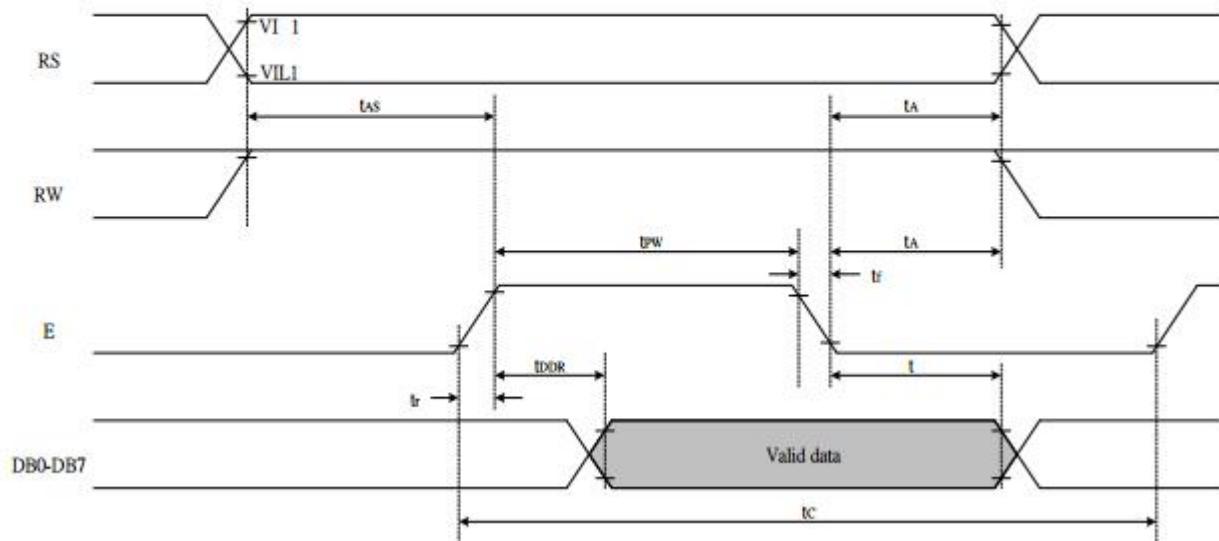

### ■ AC Characteristics

(TA = 25°C, VCC = 5V)

| Symbol                                               | Characteristics       | Test Condition  | Min. | Typ. | Max. | Unit |

|------------------------------------------------------|-----------------------|-----------------|------|------|------|------|

| <i>Internal Clock Operation</i>                      |                       |                 |      |      |      |      |

| $f_{osc}$                                            | OSC Frequency         | R = 91KΩ        | 190  | 270  | 350  | KHz  |

| <i>External Clock Operation</i>                      |                       |                 |      |      |      |      |

| $f_{EX}$                                             | External Frequency    | -               | 125  | 270  | 410  | KHz  |

|                                                      | Duty Cycle            | -               | 45   | 50   | 55   | %    |

| $T_R, T_F$                                           | Rise/Fall Time        | -               | -    | -    | 0.2  | μs   |

| <i>Write Mode (Writing data from MPU to ST7066U)</i> |                       |                 |      |      |      |      |

| $T_C$                                                | Enable Cycle Time     | Pin E           | 1200 | -    | -    | ns   |

| $T_{PW}$                                             | Enable Pulse Width    | Pin E           | 140  | -    | -    | ns   |

| $T_R, T_F$                                           | Enable Rise/Fall Time | Pin E           | -    | -    | 25   | ns   |

| $T_{AS}$                                             | Address Setup Time    | Pins: RS,RW,E   | 0    | -    | -    | ns   |

| $T_{AH}$                                             | Address Hold Time     | Pins: RS,RW,E   | 10   | -    | -    | ns   |

| $T_{DSW}$                                            | Data Setup Time       | Pins: DB0 - DB7 | 40   | -    | -    | ns   |

| $T_H$                                                | Data Hold Time        | Pins: DB0 - DB7 | 10   | -    | -    | ns   |

| <i>Read Mode (Reading Data from ST7066U to MPU)</i>  |                       |                 |      |      |      |      |

| $T_C$                                                | Enable Cycle Time     | Pin E           | 1200 | -    | -    | ns   |

| $T_{PW}$                                             | Enable Pulse Width    | Pin E           | 140  | -    | -    | ns   |

| $T_R, T_F$                                           | Enable Rise/Fall Time | Pin E           | -    | -    | 25   | ns   |

| $T_{AS}$                                             | Address Setup Time    | Pins: RS,RW,E   | 0    | -    | -    | ns   |

| $T_{AH}$                                             | Address Hold Time     | Pins: RS,RW,E   | 10   | -    | -    | ns   |

| $T_{DDR}$                                            | Data Setup Time       | Pins: DB0 - DB7 | -    | -    | 100  | ns   |

| $T_H$                                                | Data Hold Time        | Pins: DB0 - DB7 | 10   | -    | -    | ns   |

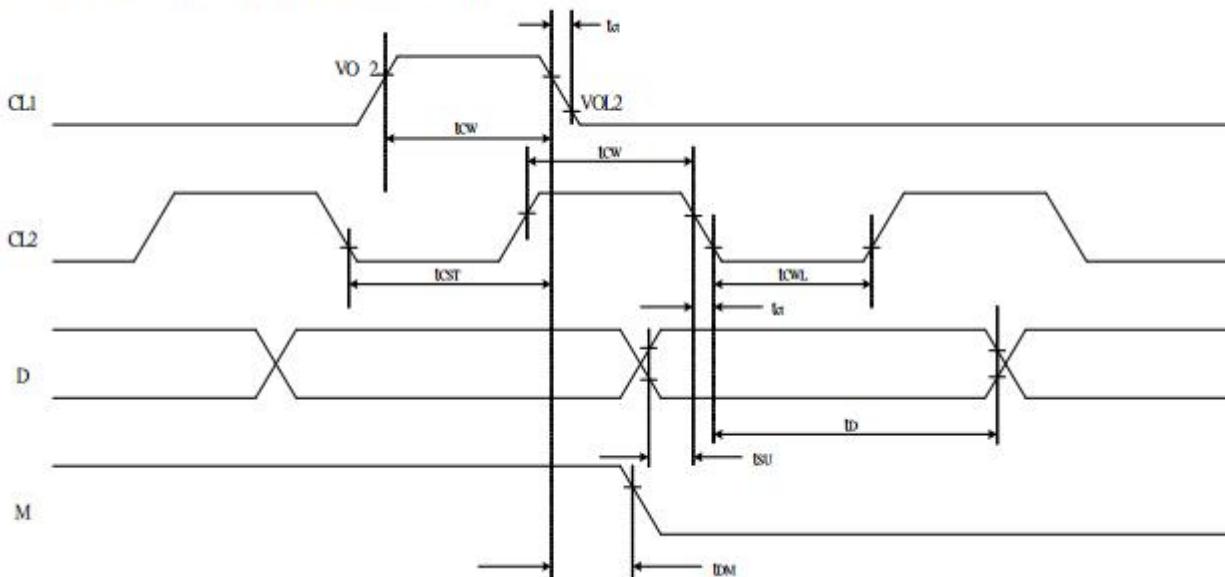

| <i>Interface Mode with LCD Driver(ST7065)</i>        |                       |                 |      |      |      |      |

| $T_{CWH}$                                            | Clock Pulse with High | Pins: CL1, CL2  | 800  | -    | -    | ns   |

| $T_{CWL}$                                            | Clock Pulse with Low  | Pins: CL1, CL2  | 800  | -    | -    | ns   |

| $T_{CST}$                                            | Clock Setup Time      | Pins: CL1, CL2  | 500  | -    | -    | ns   |

| $T_{SU}$                                             | Data Setup Time       | Pin: D          | 300  | -    | -    | ns   |

| $T_{DH}$                                             | Data Hold Time        | Pin: D          | 300  | -    | -    | ns   |

| $T_{DM}$                                             | M Delay Time          | Pin: M          | 0    | -    | 2000 | ns   |

## ■ DC Characteristics

( TA = 25°C , V<sub>CC</sub> = 4.5 V - 5.5 V )

| Symbol            | Characteristics                           | Test Condition                                     | Min.               | Typ. | Max.               | Unit |

|-------------------|-------------------------------------------|----------------------------------------------------|--------------------|------|--------------------|------|

| V <sub>CC</sub>   | Operating Voltage                         | -                                                  | 4.5                | -    | 5.5                | V    |

| V <sub>LCD</sub>  | LCD Voltage                               | V <sub>CC</sub> -V5                                | 3.0                | -    | 10.0               | V    |

| I <sub>CC</sub>   | Power Supply Current                      | f <sub>osc</sub> = 270KHz<br>V <sub>CC</sub> =5.0V | -                  | 0.2  | 0.5                | mA   |

| V <sub>IH1</sub>  | Input High Voltage<br>(Except OSC1)       | -                                                  | 0.7V <sub>CC</sub> | -    | V <sub>CC</sub>    | V    |

| V <sub>IL1</sub>  | Input Low Voltage<br>(Except OSC1)        | -                                                  | -0.3               | -    | 0.6                | V    |

| V <sub>IH2</sub>  | Input High Voltage<br>(OSC1)              | -                                                  | V <sub>CC</sub> -1 | -    | V <sub>CC</sub>    | V    |

| V <sub>IL2</sub>  | Input Low Voltage<br>(OSC1)               | -                                                  | -                  | -    | 1.0                | V    |

| V <sub>OH1</sub>  | Output High Voltage<br>(DB0 - DB7)        | I <sub>OH</sub> = -0.1mA                           | 3.9                | -    | V <sub>CC</sub>    | V    |

| V <sub>OL1</sub>  | Output Low Voltage<br>(DB0 - DB7)         | I <sub>OL</sub> = 0.1mA                            | -                  | -    | 0.4                | V    |

| V <sub>OH2</sub>  | Output High Voltage<br>(Except DB0 - DB7) | I <sub>OH</sub> = -0.04mA                          | 0.9V <sub>CC</sub> | -    | V <sub>CC</sub>    | V    |

| V <sub>OL2</sub>  | Output Low Voltage<br>(Except DB0 - DB7)  | I <sub>OL</sub> = 0.04mA                           | -                  | -    | 0.1V <sub>CC</sub> | V    |

| R <sub>COM</sub>  | Common Resistance                         | V <sub>LCD</sub> = 4V, I <sub>d</sub> = 0.05mA     | -                  | 2    | 20                 | KΩ   |

| R <sub>SEG</sub>  | Segment Resistance                        | V <sub>LCD</sub> = 4V, I <sub>d</sub> = 0.05mA     | -                  | 2    | 30                 | KΩ   |

| I <sub>LEAK</sub> | Input Leakage Current                     | V <sub>IN</sub> = 0V to V <sub>CC</sub>            | -1                 | -    | 1                  | μA   |

| I <sub>PUP</sub>  | Pull Up MOS Current                       | V <sub>CC</sub> = 5V                               | -50                | -110 | -180               | μA   |

## 7. Absolute Maximum Ratings For Bottom LED Backlight

| Parameter                       | Symbol         | Test condition       | Min | Type | Max | Unit |

|---------------------------------|----------------|----------------------|-----|------|-----|------|

| LED Forward Consumption Current | I <sub>f</sub> | T <sub>a</sub> =25°C | -   | 45   | 60  | mA   |

| LED Allowable Dissipation       | P <sub>d</sub> | V <sub>f</sub> =5V   | -   | 225  | 300 | mW   |

## 8. Pin assignment

| Pin NO. | Symbol | Function                                 | Remark  |

|---------|--------|------------------------------------------|---------|

| 1       | Vss    | Power supply                             | 0V      |

| 2       | Vdd    |                                          | +5V     |

| 3       | Vo     |                                          | For LCD |

| 4       | RS     | Register select (H: Data L: Instruction) |         |

| 5       | R/W    | L: MPU to LCM H: LCM to MPU              |         |

| 6       | E      | Enable                                   |         |

| 7       | DB0    | Data bit 0                               |         |

| 8       | DB1    | Data bit 1                               |         |

| 9       | DB2    | Data bit 2                               |         |

| 10      | DB3    | Data bit 3                               |         |

| 11      | DB4    | Data bit 4                               |         |

| 12      | DB5    | Data bit 5                               |         |

| 13      | DB6    | Data bit 6                               |         |

| 14      | DB7    | Data bit 7                               |         |

| 15      | LED-A  | Anode of LED unit                        |         |

| 16      | LED-KR | Cathode of Red LED unit                  |         |

| 17      | LED-KG | Cathode of Green LED unit                |         |

| 18      | LED-KB | Cathode of Blue LED unit                 |         |

## 9. MPU Interface (Vdd=4.5V~5.5V, Ta=-30~+85°C)

### ■ Instructions

There are four categories of instructions that:

- Designate ST7066U functions, such as display format, data length, etc.

- Set internal RAM addresses

- Perform data transfer with internal RAM

- Others

Instruction Table:

| Instruction                | Instruction Code |     |     |     |     |     |     |     |     |     |  | Description                                                                                                                      | Description Time (270KHz) |

|----------------------------|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|--|----------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|                            | RS               | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |  |                                                                                                                                  |                           |

| Clear Display              | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |  | Write "20H" to DDRAM. and set DDRAM address to "00H" from AC                                                                     | 1.52 ms                   |

| Return Home                | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | x   |  | Set DDRAM address to "00H" from AC and return cursor to its original position if shifted. The contents of DDRAM are not changed. | 1.52 ms                   |

| Entry Mode Set             | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S   |  | Sets cursor move direction and specifies display shift. These operations are performed during data write and read.               | 37 us                     |

| Display ON/OFF             | 0                | 0   | 0   | 0   | 0   | 0   | 1   | D   | C   | B   |  | D=1:entire display on<br>C=1:cursor on<br>B=1:cursor position on                                                                 | 37 us                     |

| Cursor or Display Shift    | 0                | 0   | 0   | 0   | 0   | 1   | S/C | R/L | x   | x   |  | Set cursor moving and display shift control bit, and the direction, without changing DDRAM data.                                 | 37 us                     |

| Function Set               | 0                | 0   | 0   | 0   | 1   | DL  | N   | F   | x   | x   |  | DL:interface data is 8/4 bits<br>N:number of line is 2/1<br>F:font size is 5x11/5x8                                              | 37 us                     |

| Set CGRAM address          | 0                | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |  | Set CGRAM address in address counter                                                                                             | 37 us                     |

| Set DDRAM address          | 0                | 0   | 1   | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |  | Set DDRAM address in address counter                                                                                             | 37 us                     |

| Read Busy flag and address | 0                | 1   | BF  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |  | Whether during internal operation or not can be known by reading BF. The contents of address counter can also be read.           | 0 us                      |

| Write data to RAM          | 1                | 0   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |  | Write data into internal RAM (DDRAM/CGRAM)                                                                                       | 37 us                     |

| Read data from RAM         | 1                | 1   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |  | Read data from internal RAM (DDRAM/CGRAM)                                                                                        | 37 us                     |

Note:

Be sure the ST7066U is not in the busy state (BF = 0) before sending an instruction from the MPU to the ST7066U. If an instruction is sent without checking the busy flag, the time between the first instruction and next instruction will take much longer than the instruction time itself. Refer to Instruction Table for the list of each instruction execution time.

## ■ Function Description

### ● System Interface

This chip has all two kinds of interface type with MPU : 4-bit bus and 8-bit bus. 4-bit bus or 8-bit bus is selected by DL bit in the instruction register.

During read or write operation, two 8-bit registers are used. One is data register (DR), the other is instruction register (IR).

The data register (DR) is used as temporary data storage place for being written into or read from DDRAM/CGRAM, target RAM is selected by RAM address setting instruction. Each internal operation, reading from or writing into RAM, is done automatically. So to speak, after MPU reads DR data, the data in the next DDRAM/CGRAM address is transferred into DR automatically. Also after MPU writes data to DR, the data in DR is transferred into DDRAM/CGRAM automatically.

The Instruction register (IR) is used only to store instruction code transferred from MPU. MPU cannot use it to read instruction data.

To select register, use RS input pin in 4-bit/8-bit bus mode.

| RS | R/W | Operation                                                         |

|----|-----|-------------------------------------------------------------------|

| L  | L   | Instruction Write operation (MPU writes Instruction code into IR) |

| L  | H   | Read Busy Flag (DB7) and address counter (DB0 ~ DB6)              |

| H  | L   | Data Write operation (MPU writes data into DR)                    |

| H  | H   | Data Read operation (MPU reads data from DR)                      |

Table 1. Various kinds of operations according to RS and R/W bits.

### ● Busy Flag (BF)

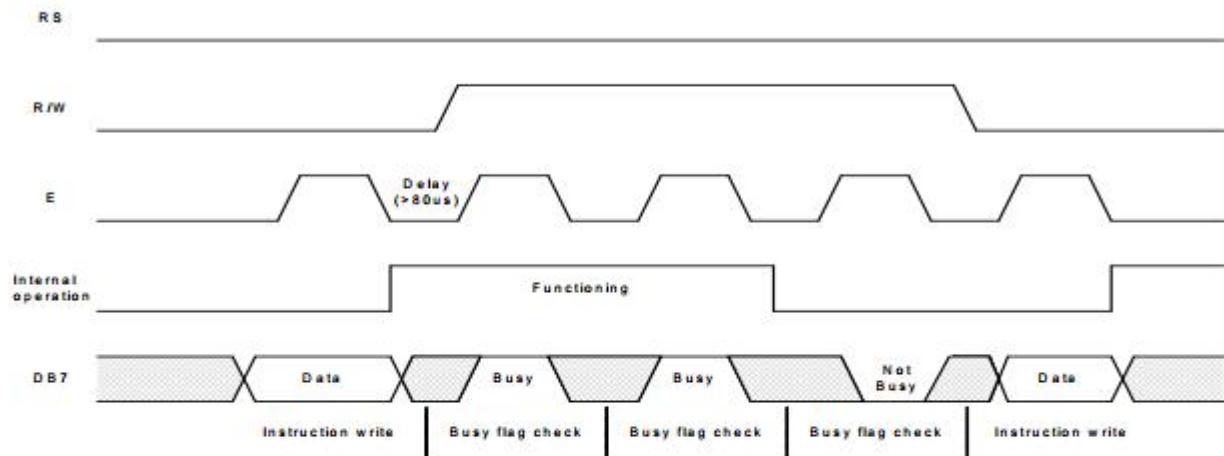

When BF = "High", it indicates that the internal operation is being processed. So during this time the next instruction cannot be accepted. BF can be read, when RS = Low and R/W = High (Read Instruction Operation), through DB7 port. Before executing the next instruction, be sure that BF is not High. Before checking BF, be sure to wait at least 80us. Please refer to Page 27 for the example. Do NOT keep "E" always "High" for checking BF.

### ● Address Counter (AC)

Address Counter (AC) stores DDRAM/CGRAM address, transferred from IR.

After writing into (reading from) DDRAM/CGRAM, AC is automatically increased (decreased) by 1. When RS = "Low" and R/W = "High", AC can be read through DB0 ~ DB6 ports.

## Timing diagram

- Writing data from MPU to ST7066U

- Reading data from ST7066U to MPU

- Interface Timing with External Driver

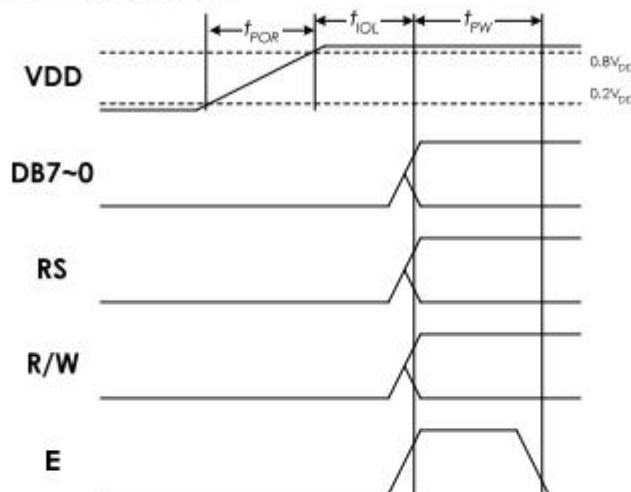

## ■ Power Supply Conditions

| Symbol | Characteristics    | Description                                                       | Min. | Typ. | Max. | Unit |

|--------|--------------------|-------------------------------------------------------------------|------|------|------|------|

| tPOR   | Power rise time    | Power rise time that will trigger internal power on reset circuit | 0.1  |      | 100  | ms   |

| tIOL   | I/O Low time       | The period that I/O is kept low.                                  | 40   |      |      | ms   |

| tPW    | Enable pulse width | Please refer to the following tables.                             |      |      |      |      |

1. During tPOR, VDD noise should be reduced (especially close to 2.0V). Otherwise the Power-ON-Reset function might be triggered several times and maybe cause unexpected result.

2. During tIOL, the I/O ports of the interface (control and data signals) should be kept at "Low".

## 10. Reflector of Screen and Display RAM

When display shift operation is performed, the DDRAM address shifts.

| Display Position | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 |

|------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| DDRAM Address    | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F |

|                  | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F |

| For Shift Left   | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E | 0F | 10 |

|                  | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E | 4F | 50 |

| For Shift Right  | 27 | 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 | 08 | 09 | 0A | 0B | 0C | 0D | 0E |

|                  | 67 | 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 4A | 4B | 4C | 4D | 4E |

2-Line by 16-Character Display Example

## 11. DISPLAY CONTROL INSTRUCTION

### ■ Instruction Description

- **Clear Display**

| RS   | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Code | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

Clear all the display data by writing "20H" (space code) to all DDRAM address, and set DDRAM address to "00H" into AC (address counter). Return cursor to the original status, namely, bring the cursor to the left edge on first line of the display. Make entry mode increment (I/D = "1").

- **Return Home**

| RS   | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Code | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | x   |

Return Home is cursor return home instruction. Set DDRAM address to "00H" into the address counter. Return cursor to its original site and return display to its original status, if shifted. Contents of DDRAM does not change.

- **Entry Mode Set**

| RS   | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |   |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| Code | 0  | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | S |

Set the moving direction of cursor and display.

- **I/D : Increment / decrement of DDRAM address (cursor or blink)**

When I/D = "High", cursor/blink moves to right and DDRAM address is increased by 1.

When I/D = "Low", cursor/blink moves to left and DDRAM address is decreased by 1.

\* CGRAM operates the same as DDRAM, when read from or write to CGRAM.

- **S: Shift of entire display**

When DDRAM read (CGRAM read/write) operation or S = "Low", shift of entire display is not performed. If S = "High" and DDRAM write operation, shift of entire display is performed according to I/D value (I/D = "1" : shift left, I/D = "0" : shift right).

| S | I/D | Description                    |

|---|-----|--------------------------------|

| H | H   | Shift the display to the left  |

| H | L   | Shift the display to the right |

- **Display ON/OFF**

| RS   | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |   |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| Code | 0  | 0   | 0   | 0   | 0   | 0   | 1   | D   | C   | B |

Control display/cursor/blink ON/OFF 1 bit register.

- **D : Display ON/OFF control bit**

When D = "High", entire display is turned on.

When D = "Low", display is turned off, but display data is remained in DDRAM.

- **C : Cursor ON/OFF control bit**

When C = "High", cursor is turned on.

When C = "Low", cursor is disappeared in current display, but I/D register remains its data.

- **B : Cursor Blink ON/OFF control bit**

When B = "High", cursor blink is on, that performs alternate between all the high data and display character at the cursor position.

When B = "Low", blink is off.

- **Cursor or Display Shift**

| RS   | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |   |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| Code | 0  | 0   | 0   | 0   | 0   | 1   | S/C | R/L | x   | x |

Without writing or reading of display data, shift right/left cursor position or display. This instruction is used to correct or search display data. During 2-line mode display, cursor moves to the 2nd line after 40th digit of 1st line. Note that display shift is performed simultaneously in all the line. When displayed data is shifted repeatedly, each line shifted individually. When display shift is performed, the contents of address counter are not changed.

| S/C | R/L | Description                                                  | AC Value |

|-----|-----|--------------------------------------------------------------|----------|

| L   | L   | Shift cursor to the left                                     | AC=AC-1  |

| L   | H   | Shift cursor to the right                                    | AC=AC+1  |

| H   | L   | Shift display to the left. Cursor follows the display shift  | AC=AC    |

| H   | H   | Shift display to the right. Cursor follows the display shift | AC=AC    |

- **Function Set**

| RS   | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |   |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| Code | 0  | 0   | 0   | 0   | 1   | DL  | N   | F   | x   | x |

➤ **DL : Interface data length control bit**

When DL = "High", it means 8-bit bus mode with MPU.

When DL = "Low", it means 4-bit bus mode with MPU. So to speak, DL is a signal to select 8-bit or 4-bit bus mode.

When 4-bit bus mode, it needs to transfer 4-bit data by two times.

➤ **N : Display line number control bit**

When N = "Low", it means 1-line display mode.

When N = "High", 2-line display mode is set.

➤ **F : Display font type control bit**

When F = "Low", it means 5 x 8 dots format display mode

When F = "High", 5 x 11 dots format display mode.

| N | F | No. of Display Lines | Character Font | Duty Factor |

|---|---|----------------------|----------------|-------------|

| L | L | 1                    | 5x8            | 1/8         |

| L | H | 1                    | 5x11           | 1/11        |

| H | x | 2                    | 5x8            | 1/16        |

● **Set CGRAM Address**

| RS   | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |     |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Code | 0  | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set CGRAM address to AC.

This instruction makes CGRAM data available from MPU.

● **Set DDRAM Address**

| RS   | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |     |

|------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Code | 0  | 0   | 1   | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

Set DDRAM address to AC.

This instruction makes DDRAM data available from MPU.

When 1-line display mode (N = 0), DDRAM address is from "00H" to "4FH".

In 2-line display mode (N = 1), DDRAM address in the 1st line is from "00H" to "27H", and DDRAM address in the 2nd line is from "40H" to "67H".

- **Read Busy Flag and Address**

|      | RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Code | 0  | 1  | BF  | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0 |

When BF = "High", indicates that the internal operation is being processed. So during this time the next instruction cannot be accepted.

The address Counter (AC) stores DDRAM/CGRAM addresses, transferred from IR.

After writing into (reading from) DDRAM/CGRAM, AC is automatically increased (decreased) by 1.

- **Write Data to CGRAM or DDRAM**

|      | RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Code | 1  | 0  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Write binary 8-bit data to DDRAM/CGRAM.

The selection of RAM from DDRAM, CGRAM, is set by the previous address set instruction : DDRAM address set, CGRAM address set. RAM set instruction can also determine the AC direction to RAM.

After write operation, the address is automatically increased/decreased by 1, according to the entry mode.

- **Read Data from CGRAM or DDRAM**

|      | RS | RW | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0 |

|------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| Code | 1  | 1  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

Read binary 8-bit data from DDRAM/CGRAM.

The selection of RAM is set by the previous address set instruction. If address set instruction of RAM is not performed before this instruction, the data that read first is invalid, because the direction of AC is not determined. If you read RAM data several times without RAM address set instruction before read operation, you can get correct RAM data from the second, but the first data would be incorrect, because there is no time margin to transfer RAM data.

In case of DDRAM read operation, cursor shift instruction plays the same role as DDRAM address set instruction : it also transfer RAM data to output data register. After read operation address counter is automatically increased/decreased by 1 according to the entry mode. After CGRAM read operation, display shift may not be executed correctly.

\* In case of RAM write operation, after this AC is increased/decreased by 1 like read operation. In this time, AC indicates the next address position, but you can read only the previous data by read instruction.

## ■ Reset Function

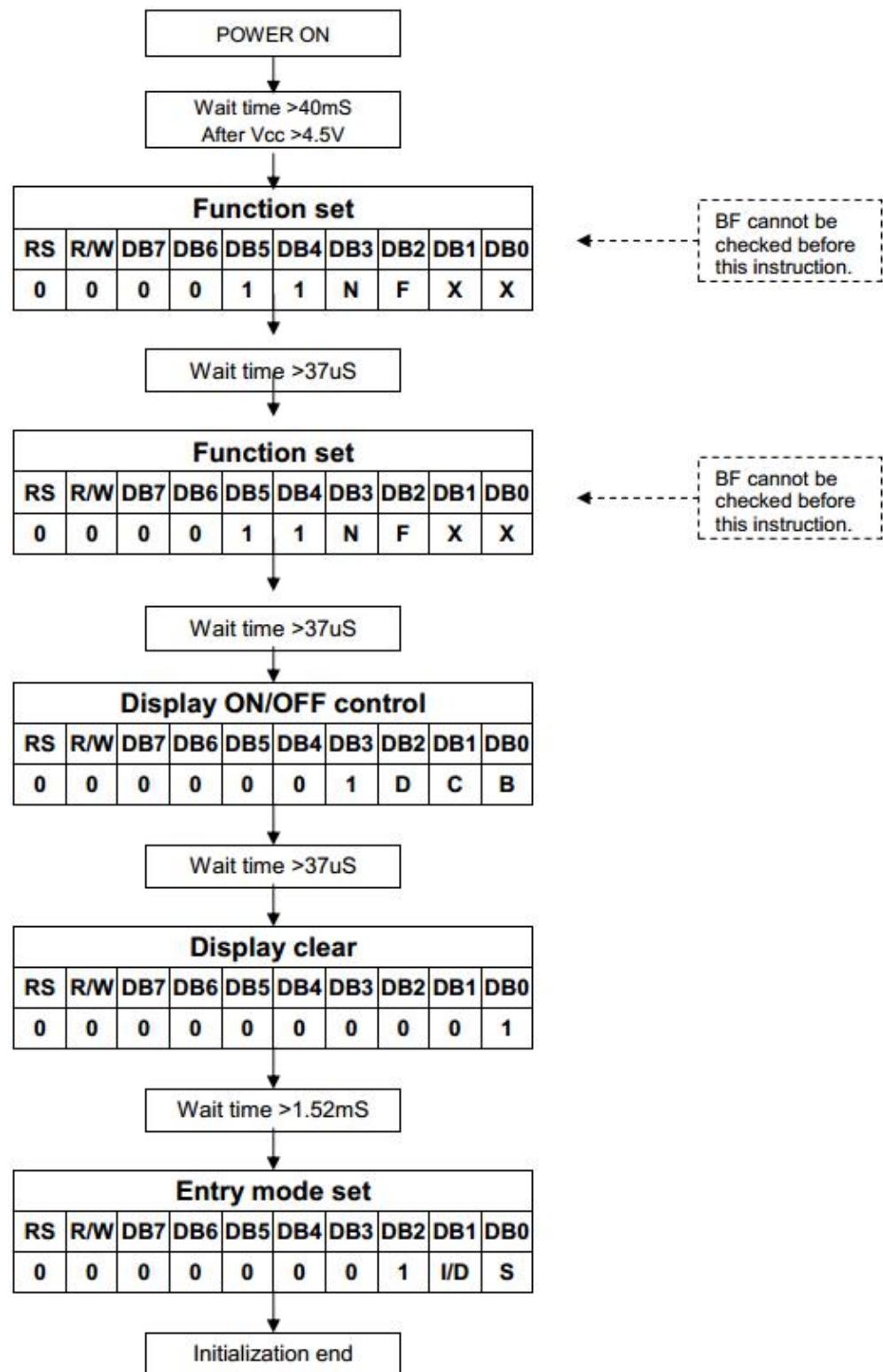

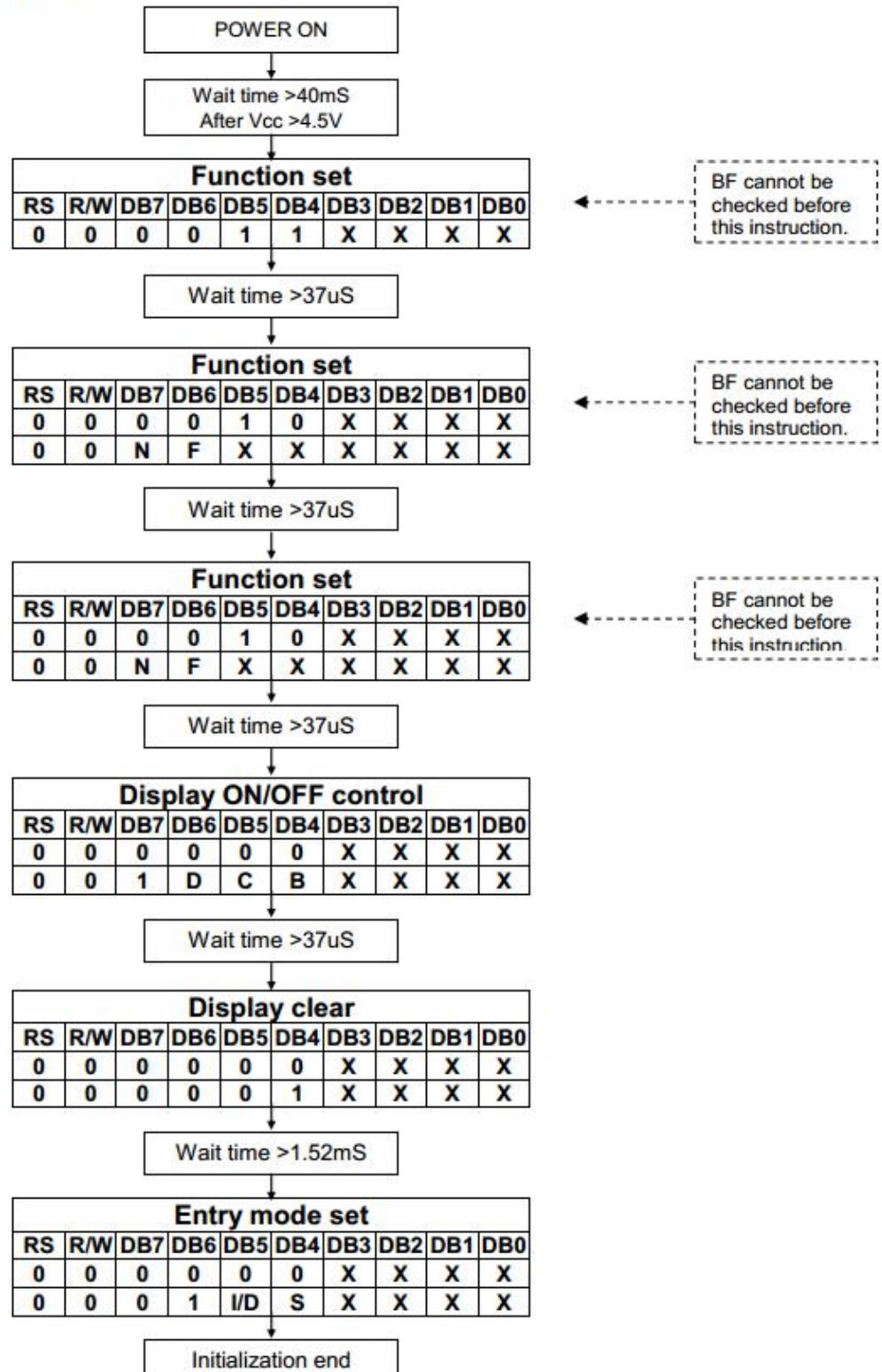

### Initializing by Internal Reset Circuit

An internal reset circuit automatically initializes the ST7066U when the power is turned on. The following instructions are executed during the initialization. The busy flag (BF) is kept in the busy state until the initialization ends (BF = 1). The busy state lasts for 40 ms after VCC rises to 4.5 V.

1. Display clear

2. Function set:

DL = 1; 8-bit interface data

N = 0; 1-line display

F = 0; 5x8 dot character font

3. Display on/off control:

D = 0; Display off

C = 0; Cursor off

B = 0; Blinking off

4. Entry mode set:

I/D = 1; Increment by 1

S = 0; No shift

**Note:**

If the electrical characteristics conditions listed in the table Power Supply Conditions (Page 31) are not met, the internal reset circuit will not operate normally and will fail to initialize the ST7066U. For such a case, initialization must be performed by the MPU as explained by the following figures.

## Relationship between Character Code and CGRAM

| Character Code<br>(DDRAM Data) |    |    |    |    |    |    |    | CGRAM<br>Address |    |    |    |    | Character Patterns<br>(CGRAM Data) |    |    |    |    |    |    |    |    |

|--------------------------------|----|----|----|----|----|----|----|------------------|----|----|----|----|------------------------------------|----|----|----|----|----|----|----|----|

| b7                             | b6 | b5 | b4 | b3 | b2 | b1 | b0 | b5               | b4 | b3 | b2 | b1 | b0                                 | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| 0                              | 0  | 0  | 0  | -  | 0  | 0  | 0  | 0                | 0  | 0  | 0  | 0  | 0                                  | -  | -  | -  | 1  | 1  | 1  | 1  | 1  |

|                                |    |    |    |    | 0  | 0  | 0  |                  |    |    | 0  | 0  | 1                                  |    |    |    | 0  | 0  | 1  | 0  | 0  |

|                                |    |    |    |    | 0  | 0  | 0  |                  |    |    | 0  | 1  | 0                                  |    |    |    | 0  | 0  | 1  | 0  | 0  |

|                                |    |    |    |    | 0  | 0  | 0  |                  |    |    | 0  | 1  | 1                                  |    |    |    | 0  | 0  | 1  | 0  | 0  |

|                                |    |    |    |    | 0  | 0  | 0  |                  |    |    | 1  | 0  | 0                                  |    |    |    | 0  | 0  | 1  | 0  | 0  |

|                                |    |    |    |    | 0  | 0  | 0  |                  |    |    | 1  | 0  | 1                                  |    |    |    | 0  | 0  | 1  | 0  | 0  |

|                                |    |    |    |    | 0  | 0  | 0  |                  |    |    | 1  | 1  | 0                                  |    |    |    | 0  | 0  | 1  | 0  | 0  |

|                                |    |    |    |    | 0  | 0  | 0  |                  |    |    | 1  | 1  | 1                                  |    |    |    | 0  | 0  | 0  | 0  | 0  |

|                                |    |    |    |    | 0  | 0  | 1  | 0                | 0  | 1  | 0  | 0  | 0                                  | -  | -  | -  | 1  | 1  | 1  | 1  | 0  |

|                                |    |    |    |    | 0  | 0  | 1  |                  |    |    | 0  | 0  | 1                                  |    |    |    | 1  | 0  | 0  | 0  | 1  |

**Table 5 Relationship between CGRAM Addresses, Character Codes (DDRAM) and Character patterns (CGRAM Data)**

Notes:

1. Character code bits 0 to 2 correspond to CGRAM address bits 3 to 5 (3 bits: 8 types).

2. CGRAM address bits 0 to 2 designate the character pattern line position. The 8th line is the cursor position and its display is formed by a logical OR with the cursor. Maintain the 8th line data, corresponding to the cursor display position, at 0 as the cursor display. If the 8th line data is 1, 1 bits will light up the 8th line regardless of the cursor presence.

3. Character pattern row positions correspond to CGRAM data bits 0 to 4 (bit 4 being at the left).

4. As shown Table 5, CGRAM character patterns are selected when character code bits 4 to 7 are all 0. However, since character code bit 3 has no effect, the R display example above can be selected by either character code 00H or 08H.

5. 1 for CGRAM data corresponds to display selection and 0 to non-selection.

"-": Indicates no effect.

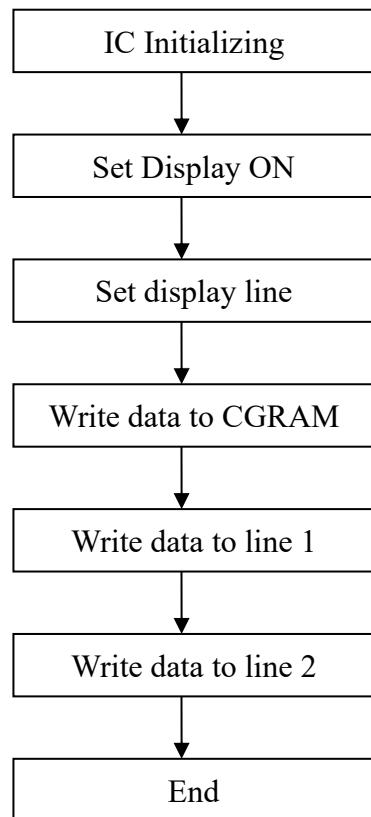

## ■ Initializing by Instruction

- 8-bit Interface (fosc=270KHz)

● 4-bit Interface (fosc=270KHz)

## 12.OPTICAL CHARACTERISTICS:

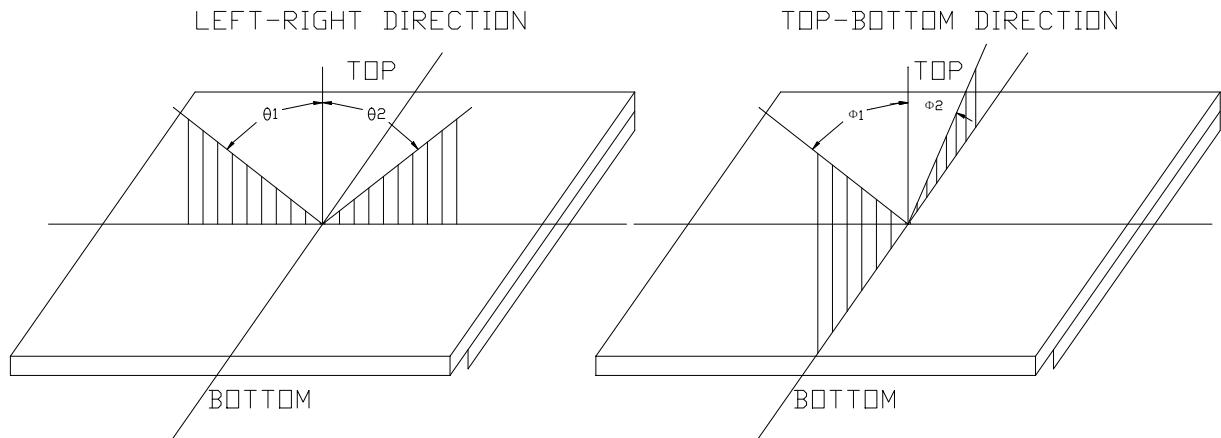

### (1)Definition of viewing Angle:

### (2)Definition of Contrast Ratio:

$$\text{Contrast Ratio} = \frac{\text{Brightness of non-selected condition}}{\text{Brightness of selected condition}}$$

Test condition: standard A light source

### (3)Response Time:

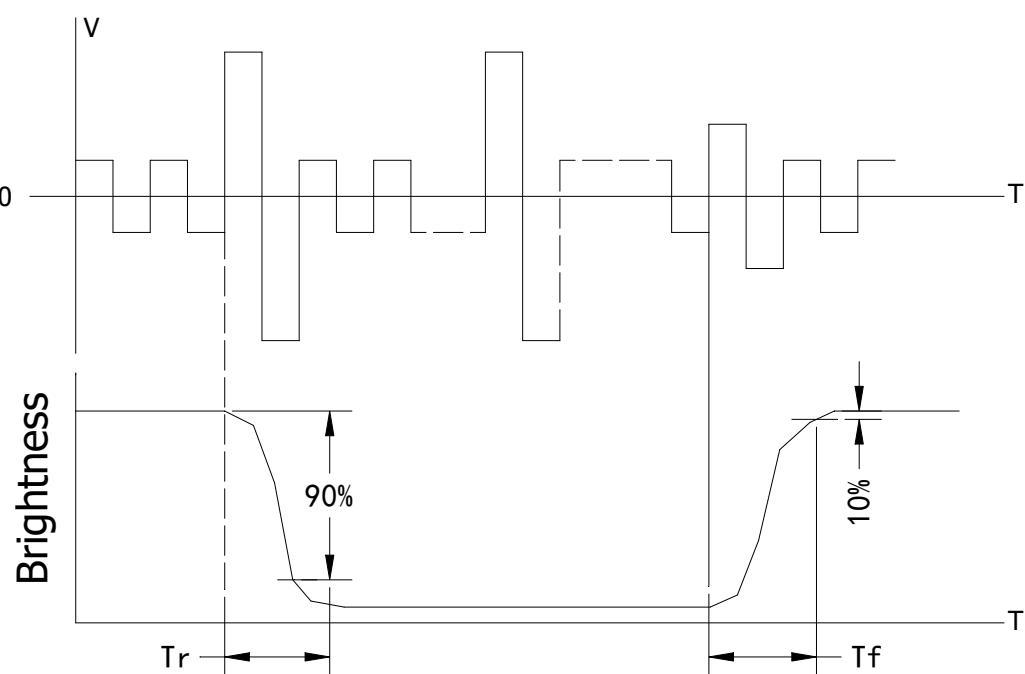

Response time is measured as the shortest period of possible between the change in state of an LCD segments as demonstrated below:

## 13. POWER SUPPLY SCHEMATICS

### ■ Supply Voltage for LCD Drive

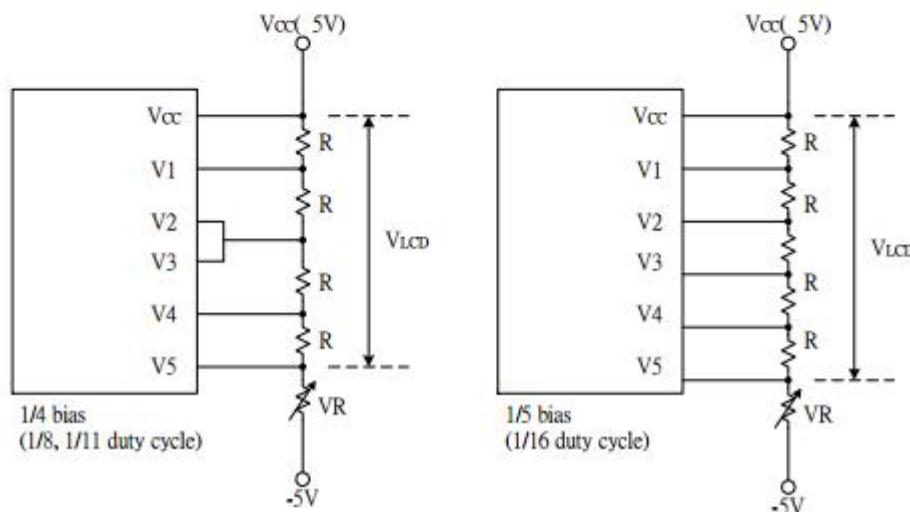

There are different voltages that supply to ST7066U's pin (V1 - V5) to obtain LCD drive waveform. The relations of the bias, duty factor and supply voltages are shown as below:

| Supply Voltage | Duty Factor                           |                                       |

|----------------|---------------------------------------|---------------------------------------|

|                | 1/8, 1/11                             | 1/16                                  |

|                | Bias                                  |                                       |

| V1             | V <sub>cc</sub> - 1/4V <sub>LCD</sub> | V <sub>cc</sub> - 1/5V <sub>LCD</sub> |

| V2             | V <sub>cc</sub> - 1/2V <sub>LCD</sub> | V <sub>cc</sub> - 2/5V <sub>LCD</sub> |

| V3             | V <sub>cc</sub> - 1/2V <sub>LCD</sub> | V <sub>cc</sub> - 3/5V <sub>LCD</sub> |

| V4             | V <sub>cc</sub> - 3/4V <sub>LCD</sub> | V <sub>cc</sub> - 4/5V <sub>LCD</sub> |

| V5             | V <sub>cc</sub> - V <sub>LCD</sub>    | V <sub>cc</sub> - V <sub>LCD</sub>    |

## 14. APPLICATION EXAMPLE

### Application Circuit

- For 8-bit interface data, all eight bus lines (DB0 to DB7) are used.

➤ Example of busy flag check timing sequence

➤ Intel 8051 interface

## Application Flowchart

## Correspondence between Character Codes and Character Patterns (ROM Code: 0A)

NO.7066-0A

| b7-b4<br>b3-b0   | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

|------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| CG<br>RAM<br>(1) |      |      |      | 8    | 9    | F    | 8    | P    |      |      |      |      | 8    | 9    | 8    | P    |

| 0000             |      |      |      | 1    | 8    | 9    | a    | 9    |      |      |      |      | 8    | 9    | 8    | 9    |

| 0001             | (2)  |      |      | 2    | 8    | B    | B    | b    |      |      |      |      | 8    | 9    | 8    | 9    |

| 0010             | (3)  |      |      | 3    | 8    | C    | S    | c    |      |      |      |      | 8    | 9    | 8    | 9    |

| 0011             | (4)  |      |      | 4    | 8    | D    | T    | d    |      |      |      |      | 8    | 9    | 8    | 9    |

| 0100             | (5)  |      |      | 5    | 8    | E    | U    | e    | u    |      |      |      | 8    | 9    | 8    | 9    |

| 0101             | (6)  |      |      | 6    | 8    | F    | V    | f    | v    |      |      |      | 8    | 9    | 8    | 9    |

| 0110             | (7)  |      |      | 7    | 8    | G    | W    | g    | w    |      |      |      | 8    | 9    | 8    | 9    |

| 0111             | (8)  |      |      | 8    | 8    | H    | X    | h    | x    |      |      |      | 8    | 9    | 8    | 9    |

| 1000             | (1)  |      |      | 9    | 8    | I    | Y    | i    | y    |      |      |      | 8    | 9    | 8    | 9    |

| 1001             | (2)  |      |      | +    | 8    | J    | Z    | j    | z    |      |      |      | 8    | 9    | 8    | 9    |

| 1010             | (3)  |      |      | *    | 8    | K    | C    | k    | c    |      |      |      | 8    | 9    | 8    | 9    |

| 1011             | (4)  |      |      | #    | 8    | L    | Y    | l    | y    |      |      |      | 8    | 9    | 8    | 9    |

| 1100             | (5)  |      |      | -    | 8    | M    | J    | m    | j    |      |      |      | 8    | 9    | 8    | 9    |

| 1101             | (6)  |      |      | =    | 8    | N    | ^    | n    | ^    |      |      |      | 8    | 9    | 8    | 9    |

| 1110             | (7)  |      |      | *    | 8    | ?    | 0    | o    | *    |      |      |      | 8    | 9    | 8    | 9    |

| 1111             | (8)  |      |      | X    | 8    | 0    | _    | o    | *    |      |      |      | 8    | 9    | 8    | 9    |

## 15. PRECAUTION FOR USING LCM

### 1. Liquid Crystal Display (LCD)

LCD is made up of glass, organic sealant, organic fluid, and polymer based polarizers. The following precautions should be taken when handing,

- (1). Keep the temperature within range of use and storage. Excessive temperature and humidity could cause polarization degradation, polarizer peel off or bubble.

- (2). Do not contact the exposed polarizers with anything harder than an HB pencil lead. To clean dust off the display surface. Wipe gently with cotton. Chamois or other soft material soaked in petroleum benzine.

- (3). Wipe off saliva or water drops immediately. Contact with water over a long period of time may cause polarizer deformation or color fading, while an active LCD with water condensation on its surface will cause corrosion of ITO electrodes.

- (4). Glass can be easily chipped or cracked from rough handing. especially at corners and edges.

- (5). Do not drive LCD with DC voltage.

### 2. Liquid Crystal Display Modules

#### 2.1 Mechanical Considerations

LCM are assembled and adjusted with a high degree of precision. Avoid excessive shocks and do not make any alterations or modifications. The following should be noted.

- (1). Do not tamper in any way with the tabs on the tabs on the metal frame.

- (2). Do not modify the PCB by drilling extra holes, changing its outline, moving its components or modifying its pattern.

- (3). Do not touch the elastomer connector, especially insert an backlight panel (for example, EL).

- (4). When mounting a LCM make sure that the PCB is not under any stress such as bending or twisting. Elastomer contacts are very delicate and missing pixels could result from slight dislocation of any of the elements.

- (5). Avoid pressing on the metal bezel, otherwise the elastomer connector could be deformed and lose contact, resulting in missing pixels.

#### 2.2. Static Electricity

LCM contains CMOS LSI's and the same precaution for such devices should apply, namely

- (1). The operator should be grounded whenever he/she comes into contact with the module. Never touch any of the conductive parts such as the LSI pads, the copper leads on the PCB and the interface terminals with any parts of the human body.

- (2). The modules should be kept in antistatic bags or other containers resistant to static for storage.

- (3). Only properly grounded soldering irons should be used.

- (4). If an electric screwdriver is used, it should be well grounded and shielded from commutator sparks.

- (5). The normal static prevention measures should be observed for work clothes and working benches; for the latter conductive ( rubber) mat is recommended.

- (6). Since dry air is inductive to static, a relative humidity of 50-60% is recommended.

#### 2.3. Soldering

- (1). Solder only to the I/O terminals.

- (2). Use only soldering irons with proper grounding and no leakage.

- (3). Soldering temperature:  $280^{\circ}\text{C} \pm 10^{\circ}\text{C}$

- (4). Soldering time: 3 to 4 sec.

- (5). Use eutectic solder with resin flux fill.

- (6). If flux is used, the LCD surface should be covered to avoid flux spatters. Flux residue should be removed afterwards.

#### 2.4. Operation

- (1). The viewing angle can be adjusted by varying the LCD driving voltage  $V_0$ .

- (2). Driving voltage should be kept within specified range; excess voltage shortens display life.

- (3). Response time increases with decrease in temperature.

- (4). Display may turn black or dark blue at temperatures above its operational range; this is (however not pressing on the viewing area) may cause the segments to appear "fractured".

(5). Mechanical disturbance during operation (such as pressing on the viewing area) may cause the segments to appear “fractured”.

## **2.5. Storage**

If any fluid leaks out of a damaged glass cell, wash off any human part that comes into contact with soap and water. Never swallow the fluid. The toxicity is extremely low but caution should be exercised at all the time.

## **2.6. Limited Warranty**

Unless otherwise agreed between SHEN ZHEN TEAM SOURCE DISPLAY TECH. CO.,LTD. and customer, SSHEN ZHEN TEAM SOURCE DISPLAY TECH. CO.,LTD will repair or repair any of its LCD and IC, which is found to be defective electrically and visually when inspected in accordance with SHEN ZHEN TEAM SOURCE DISPLAY TECH. CO.,LTD. acceptance standards, for a period on one year from date of shipment. Confirmation of such date shall be based on freight documents. The warranty liability of SHEN ZHEN TEAM SOURCE DISPLAY TECH. CO.,LTD. is limited to repair and/or replacement on the terms set forth above. SHEN ZHEN TEAM SOURCE DISPLAY TECH. CO.,LTD. will not responsible for any subsequent or consequential events.