## 特征

- 单电源供电: 2.7V~5.5V

- 低电源电流: 120 $\mu$ A

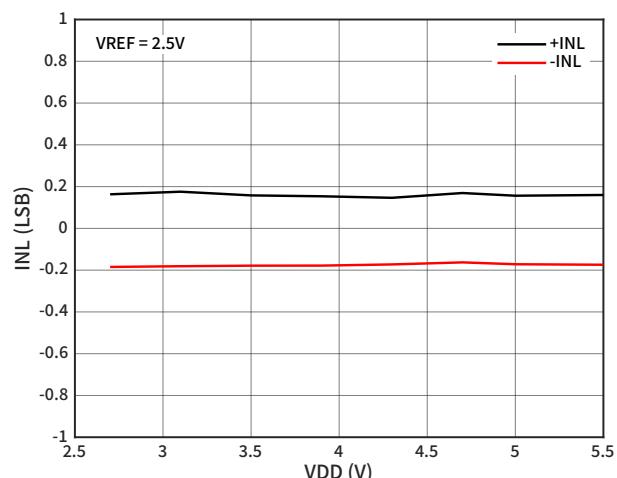

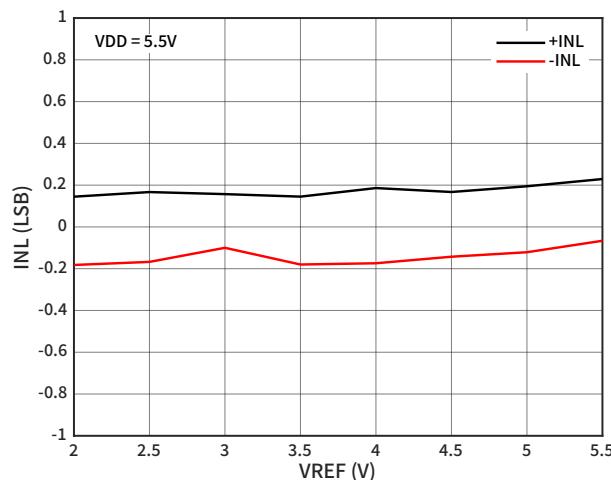

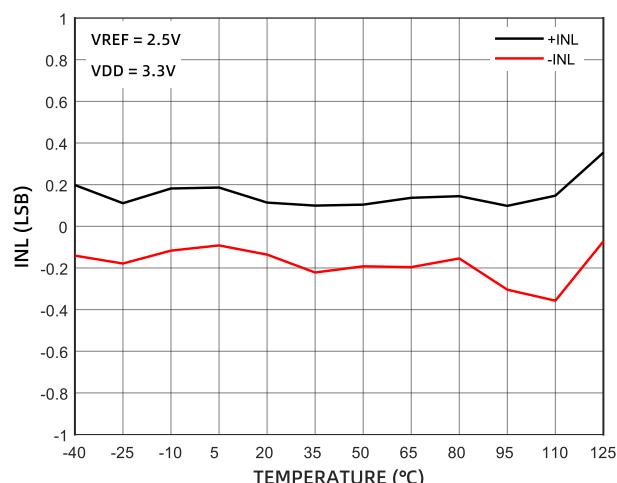

- INL 误差:  $\pm 0.4$ LSB

- 低毛刺脉冲: 0.5nV·s

- 短建立时间: 1 $\mu$ s

- 全温范围内保证输出电压单调性

- 电压输出可直接驱动 60k $\Omega$  负载

- 50MHz SPI/QSPI/MICROWIRE 兼容型串行接口

- 上电复位将 DAC 输出至中间电平

- CLR 异步复位管脚

- 补偿基准源电流

- MSOP10 3mm × 3mm、DFN10 3mm × 3mm 封装

## 应用

- 激光振镜控制器

- 高精度仪器仪表校准电路

- 过程控制和工业自动化

- 自动测试设备

- 精密信号源

## 概述

CM7502L 是一款 16 位无缓冲电压输出数模转换器 (DAC)。采用 2.7V 至 5.5V 单电源供电, 可在全温范围内保证输出电压的单调性。无缓冲器的设计, 使得 DAC 具有极低的功耗, 仅有 120 $\mu$ A 的静态电流, 以及 0.5LSB 的低零码失调误差。

CM7502L 均支持 2V 至 VDD 的基准电压输入范围。电压输出摆幅为 0V 至 VREF。CM7502L 内部集成了精确匹配的电阻串, 通过与片外精密运算放大器配合, 可在 RFB 上产生最大  $\pm VREF$  摆幅的双极性电压输出。

CM7502L 采用 SPI/QSPI/MICROWIRE 兼容型三线串行接口, 能够以高达 50MHz 的时钟速率运行, 并可直接与光耦合器相连, 以满足特定应用的需求。上电时, 复位电路将 CM7502L 输出至中间电平。CLR 也可将 CM7502L 输出至中间电平。

CM7502L 仅支持在双极性输出模式下工作。

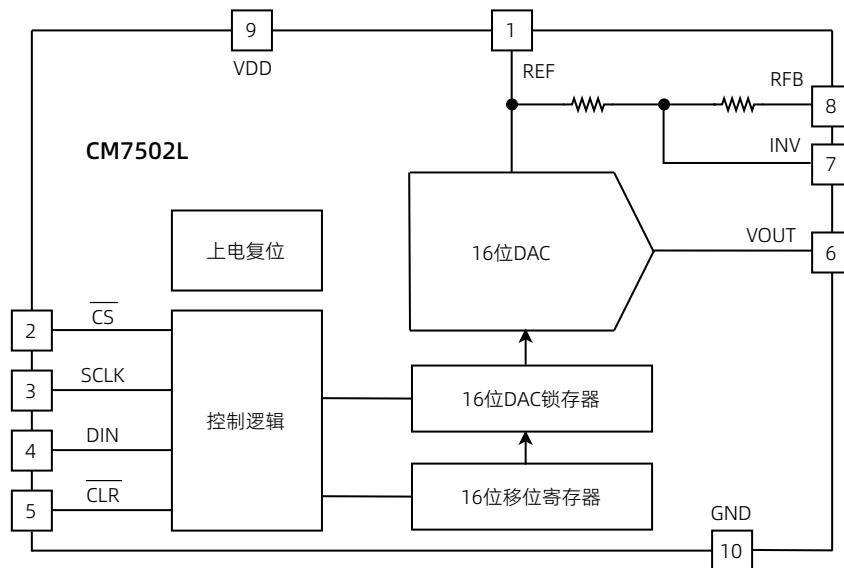

## 架构框图

# 目录

|                     |    |                     |    |

|---------------------|----|---------------------|----|

| 封页                  | 1  | 电压输出建立时间            | 13 |

| 特征                  | 1  | 运算放大器               | 13 |

| 应用                  | 1  | 运算放大器规格和 CM7502L 精度 | 13 |

| 概述                  | 1  | 电压输出建立时间 (使用运算放大器时) | 14 |

| 架构框图                | 1  | 电压基准                | 14 |

| 文档历史                | 3  | 复位                  | 14 |

| 管脚配置和功能             | 4  | 数字接口                | 15 |

| 管脚配置 (MSOP10/DFN10) | 4  | 串行接口                | 15 |

| 管脚功能 (MSOP10/DFN10) | 4  | 数字输入和接口逻辑           | 15 |

| 绝对最大额定值             | 5  | 应用                  | 16 |

| 电气规格                | 6  | 封装及订购信息             | 17 |

| 时序规格                | 8  | 封装方式                | 17 |

| 典型特征                | 9  | 产品外形图               | 17 |

| 工作原理                | 13 | MSOP10              | 17 |

| DAC 结构              | 13 | DFN10               | 18 |

| 负载对 DAC 输出电压精度的影响   | 13 | 订购信息                | 19 |

## 文档历史

下表列举了本文档自产品发布后的所有更新。

| 文档版本 | 修订日期       | 内容描述                      |

|------|------------|---------------------------|

| V1.0 | 2024-06-21 | 初版发布。                     |

| V1.1 | 2025-04-01 | 更新 <a href="#">电气规格</a> 。 |

## 管脚配置和功能

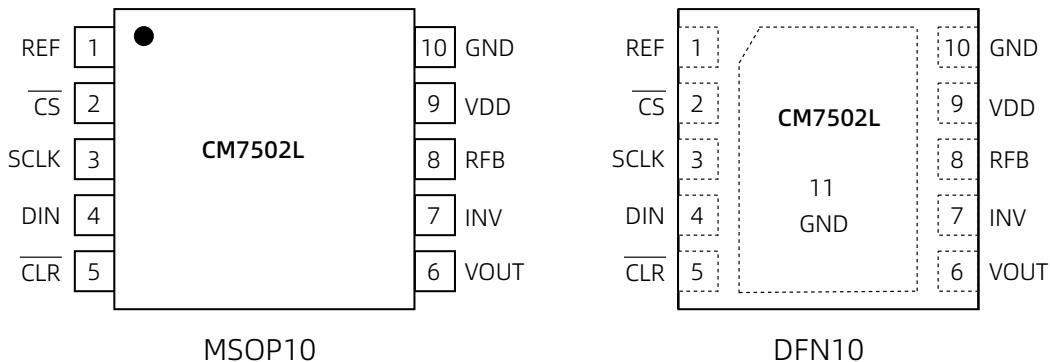

### 管脚配置 (MSOP10/DFN10)

以下为 CM7502L MSOP10 和 DFN10 封装管脚示意图。

### 管脚功能 (MSOP10/DFN10)

| 编号 | 名称               | 类型  | 说明                                                                                             |

|----|------------------|-----|------------------------------------------------------------------------------------------------|

| 1  | REF              | A   | 基准电压输入。可输入一个 2V 至 VDD 的外部基准电压。                                                                 |

| 2  | $\overline{CS}$  | DI  | 串行接口片选。当 $\overline{CS}$ 位于低电平时，数据通过 DIN 串行输入。当 $\overline{CS}$ 变为高电平时，16 位输入被锁存，并更新 DAC 输出电压。 |

| 3  | SCLK             | DI  | 串行接口时钟。兼容 CMOS 和 TTL 两种逻辑电平。                                                                   |

| 4  | DIN              | DI  | 串行接口数据。                                                                                        |

| 5  | $\overline{CLR}$ | DI  | 异步复位输入。逻辑低电平将 CM7502L 输出复位至中间电平。                                                               |

| 6  | VOUT             | AO  | 电压输出。范围为 0V 至 VREF。                                                                            |

| 7  | INV              | A   | 电阻器中心抽头。与外部放大器的反向输入相连接。                                                                        |

| 8  | RFB              | A   | 反馈电阻。与外部放大器的输出相连接，输出范围为 -VREF 至 VREF。                                                          |

| 9  | VDD              | PWR | 电源输入。范围为 2.7V 至 5.5V。                                                                          |

| 10 | GND              | GND | 地。                                                                                             |

| 11 | EPAD             | GND | 无内部电气连接，建议焊接到地平面。                                                                              |

## 绝对最大额定值

| 参数                                                | 最小值                 | 最大值         | 单位 |

|---------------------------------------------------|---------------------|-------------|----|

| <b>温度</b>                                         |                     |             |    |

| 工作温度                                              | -40                 | 125         | °C |

| 存储温度                                              | -65                 | 150         | °C |

| 结温                                                |                     | 150         | °C |

| 回流焊                                               | 铅锡焊接温度 (10 秒到 30 秒) | 240         | °C |

|                                                   | 无铅焊接温度              | 260         | °C |

| <b>耐压</b>                                         |                     |             |    |

| VDD 至 GND                                         | -0.3                | 6           | V  |

| $\overline{CS}$ 、SCLK、DIN、 $\overline{CLR}$ 至 GND | -0.3                | $VDD + 0.3$ | V  |

| REF、VOUT、INV 至 GND                                | -0.3                | $VDD + 0.3$ | V  |

| RFB 至 RINV/GND                                    | -6                  | 6           | V  |

| <b>ESD</b>                                        |                     |             |    |

| HBM                                               | 4000                |             | V  |

| CDM                                               | 1000                |             | V  |

注1： 使用本表以外的数值可能会对芯片造成永久性损坏。长时间暴露于本表数值下可能会影响芯片的稳定性和使用寿命。

注2： 持续在超出指定结温下工作可能会影响芯片稳定性。

## 电气规格

默认测试条件: VDD = 3V 或 5V、VREF = 2.5V、C<sub>L</sub> = 10pF、GND = 0、R<sub>L</sub> =  $\infty$ 、TA = -40°C~125°C。

| 参数                                        | 测试条件                                                   | 最小值         | 典型值        | 最大值 | 单位              |

|-------------------------------------------|--------------------------------------------------------|-------------|------------|-----|-----------------|

| <b>静态性能</b>                               |                                                        |             |            |     |                 |

| 分辨率                                       |                                                        | 16          |            |     | Bits            |

| 单调性                                       |                                                        | 16          |            |     | Bits            |

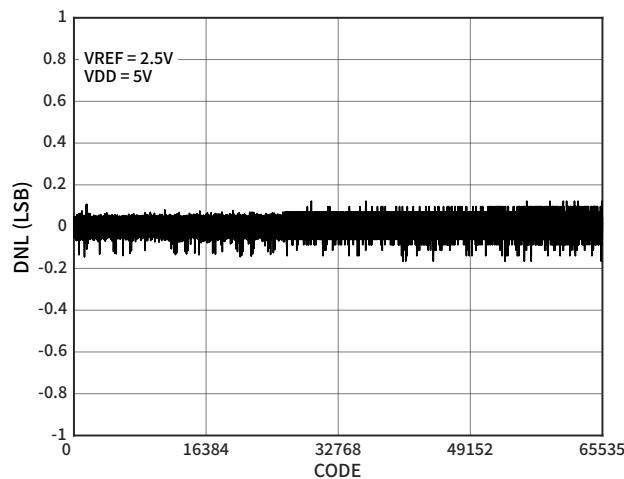

| DNL                                       |                                                        | $\pm 0.3$   | $\pm 1$    |     | LSB             |

| INL                                       |                                                        | $\pm 0.4$   | $\pm 1$    |     | LSB             |

| 零码失调误差 (ZSE)                              | CODE = 0                                               | 0.5         | 2          |     | LSB             |

| 零码失调误差温漂                                  |                                                        | $\pm 0.05$  |            |     | ppm/°C          |

| 增益误差 (GE)                                 |                                                        | $\pm 1$     | $\pm 5$    |     | LSB             |

| 增益误差温漂                                    |                                                        | $\pm 0.1$   |            |     | ppm/°C          |

| 输出阻抗 (R <sub>OUT</sub> )                  | TA = 25°C                                              | 6           |            |     | kΩ              |

| 电阻匹配 (R <sub>FB</sub> /R <sub>INV</sub> ) |                                                        | 1           |            |     |                 |

| 双极性匹配误差 <sup>1</sup>                      |                                                        | $\pm 0.002$ | $\pm 0.01$ |     | %               |

| 双极性零压失调误差                                 |                                                        | $\pm 0.5$   | $\pm 2$    |     | LSB             |

| 双极性零压失调误差温漂                               |                                                        | $\pm 0.05$  |            |     | ppm/°C          |

| PSRR                                      | $\Delta VDD = \pm 10\%$                                |             | $\pm 1$    |     | LSB             |

| <b>动态性能</b>                               |                                                        |             |            |     |                 |

| 压摆率                                       | 测试从 10% 至 90%, TA = 25°C                               | 15          |            |     | V/μs            |

| 建立时间                                      | 建立误差为 1/2LSB, TA = 25°C                                | 1           |            |     | μs              |

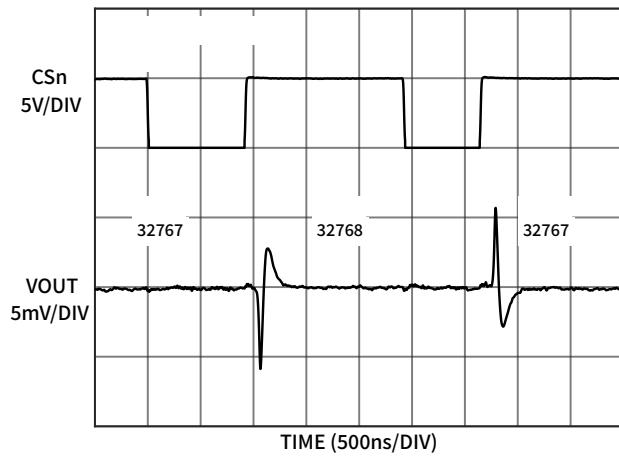

| 毛刺脉冲                                      | 主进位改变 1LSB, TA = 25°C                                  | 0.5         |            |     | nV·s            |

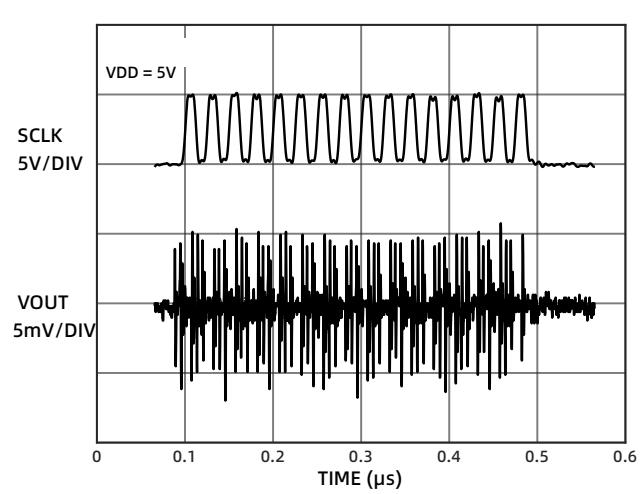

| 数字馈通                                      | CODE = 0x0000, NCS = VDD, SCLK/DIN = 0V~VDD, TA = 25°C | 0.2         |            |     | nV·s            |

| 输出电压噪声密度                                  | TA = 25°C                                              | 10          |            |     | nV/ $\sqrt{Hz}$ |

| <b>基准输入</b>                               |                                                        |             |            |     |                 |

| 电压范围                                      |                                                        | 2           | VDD        |     | V               |

| 阻抗                                        |                                                        | 12.2        |            |     | kΩ              |

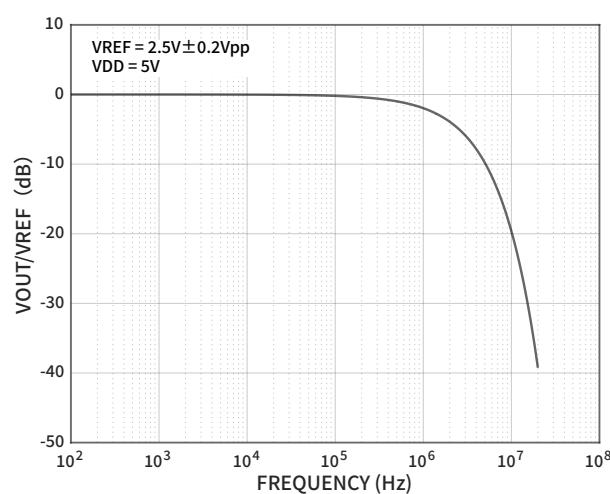

| -3dB 带宽                                   | CODE = 0xFFFF, TA = 25°C                               | 1.5         |            |     | MHz             |

| 输入馈通                                      | CODE = 0x0000, VREF = 1Vpp@100kHz, TA = 25°C           | 0.5         |            |     | mVpp            |

| SNR                                       | TA = 25°C                                              | 92          |            |     | dB              |

| 输入电容                                      | CODE = 0x0000, TA = 25°C                               | 110         |            |     | pF              |

|                                           | CODE = 0xFFFF, TA = 25°C                               | 125         |            |     | pF              |

| <b>数字输入</b>                               |                                                        |             |            |     |                 |

| 逻辑输入高电平                                   | VDD = 3.6V~5.5V                                        | 2.4         |            |     | V               |

|                                           | VDD = 2.7V~3.6V                                        | 2           |            |     | V               |

| 参数        | 测试条件                                 | 最小值  | 典型值     | 最大值 | 单位      |

|-----------|--------------------------------------|------|---------|-----|---------|

| 逻辑输入低电平   | VDD = 4.5V~5.5V                      |      | 0.8     |     | V       |

|           | VDD = 2.7V~4.5V                      |      | 0.6     |     | V       |

| 电流        | VIN = GND~VDD                        |      | $\pm 1$ |     | $\mu A$ |

| 电容        |                                      |      | 10      |     | pF      |

| 迟滞电压      | TA = 25°C                            | 0.18 |         |     | V       |

| <b>电源</b> |                                      |      |         |     |         |

| VDD       |                                      | 2.7  | 5.5     |     | V       |

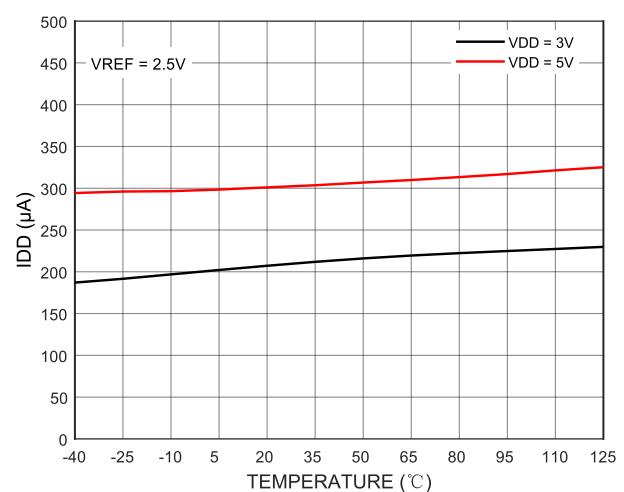

| IDD       | 数字输入 = 0V 或 VDD                      | 120  | 250     |     | $\mu A$ |

| 功耗        | 数字输入 = 0V 或 VDD, VDD = 5V, TA = 25°C | 0.6  |         |     | mW      |

|           | 数字输入 = 0V 或 VDD, VDD = 3V, TA = 25°C | 0.36 |         |     | mW      |

注1：不代表电阻自身匹配精度，该数值通过测量CM7502L双极性输出模式下的满量程误差和失调误差得到。

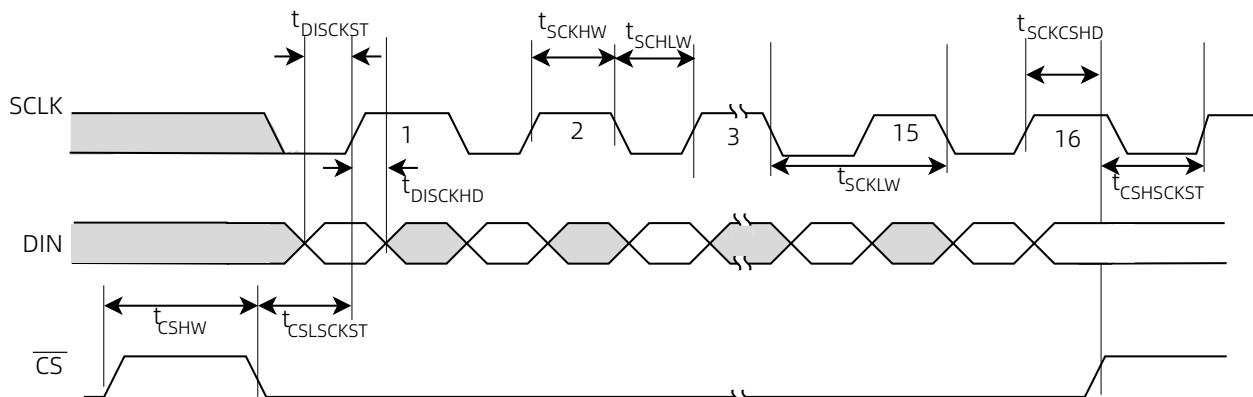

## 时序规格

| 参数              | 描述                                        | 最小值 | 典型值 | 最大值 | 单位 |

|-----------------|-------------------------------------------|-----|-----|-----|----|

| $t_{DISCKST}$   | DIN 到 SCLK 上升沿的建立时间。                      | 10  |     |     | ns |

| $t_{DISCKHD}$   | DIN 到 SCLK 上升沿的保持时间。                      | 0   |     |     | ns |

| $t_{SCKHW}$     | SCLK 高电平脉冲宽度。                             | 9   |     |     | ns |

| $t_{SCKLW}$     | SCLK 低电平脉冲宽度。                             | 9   |     |     | ns |

| $t_{CSHW}$      | $\overline{CS}$ 高电平脉冲宽度。                  | 40  | 120 |     | ns |

| $t_{SCKCSHD}$   | LSB SCLK 上升沿到 $\overline{CS}$ 高电平的保持时间。   | 8   |     |     | ns |

| $t_{CSLSCKST}$  | $\overline{CS}$ 低电平到 SCLK 上升沿的建立时间。       | 8   |     |     | ns |

| $t_{CSHSCCKST}$ | $\overline{CS}$ 高电平到 SCLK 上升沿的建立时间。       | 8   |     |     | ns |

| $t_{CLRLW}$     | $\overline{CLR}$ 低电平脉冲宽度。                 | 15  |     |     | ns |

| $t_{SCKCYC}$    | SCLK 周期。                                  | 20  | 23  |     | ns |

|                 | VDD 高电平到 $\overline{CS}$ 低电平 (上电延迟) DIST。 |     |     | 3.5 | ms |

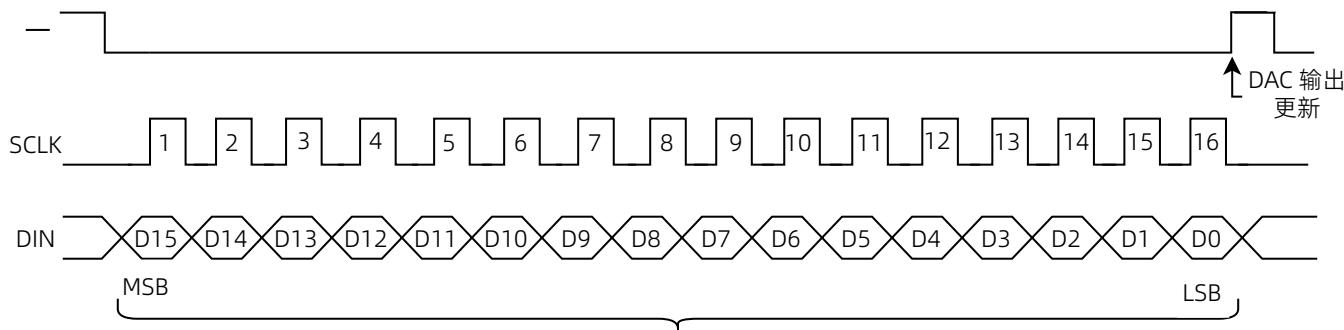

图 1 SPI 时序图

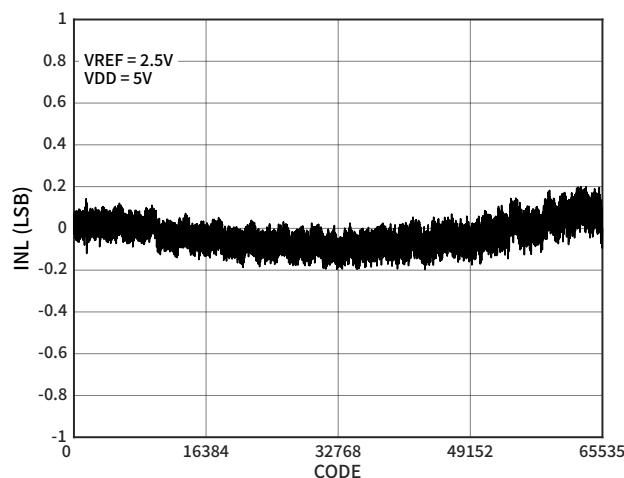

## 典型特征

图 2 INL

图 3 INL 误差随 VDD 的变化

图 4 INL 误差随 VREF 的变化

图 5 INL 误差的温度特性

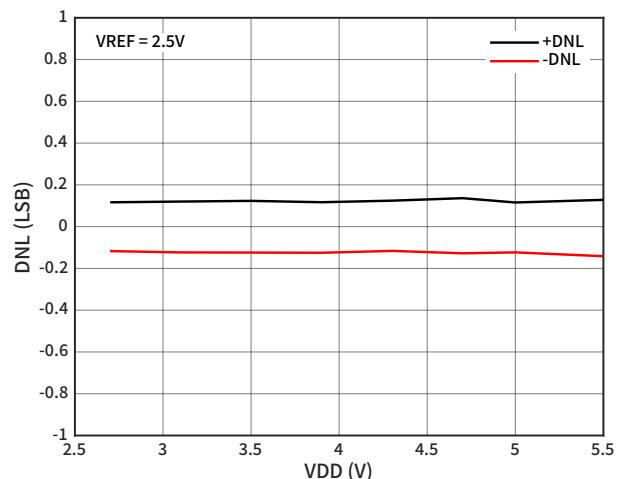

图 6 DNL

图 7 DNL 误差随 VDD 的变化

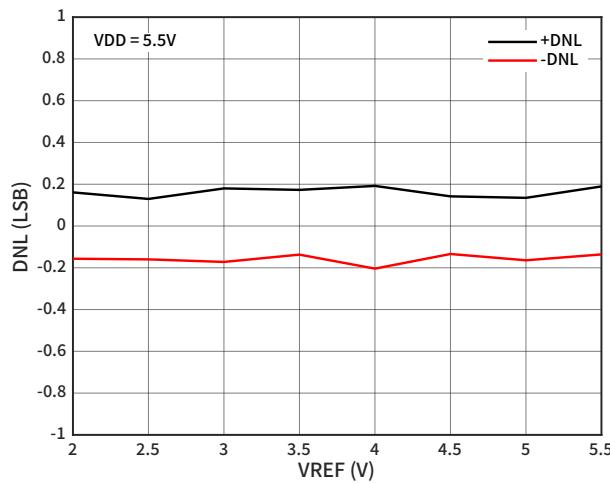

图 8 DNL 误差随 VREF 的变化

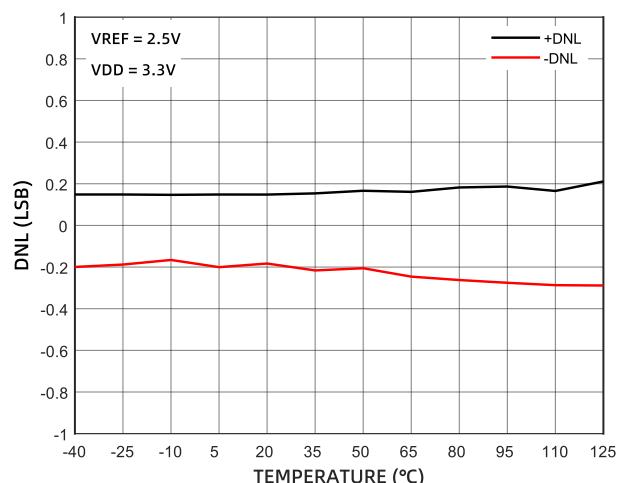

图 9 DNL 误差的温度特性

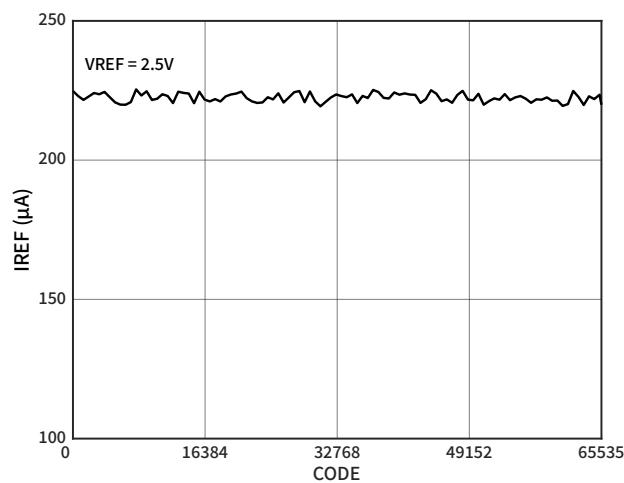

图 10 IREF 随 CODE 的变化

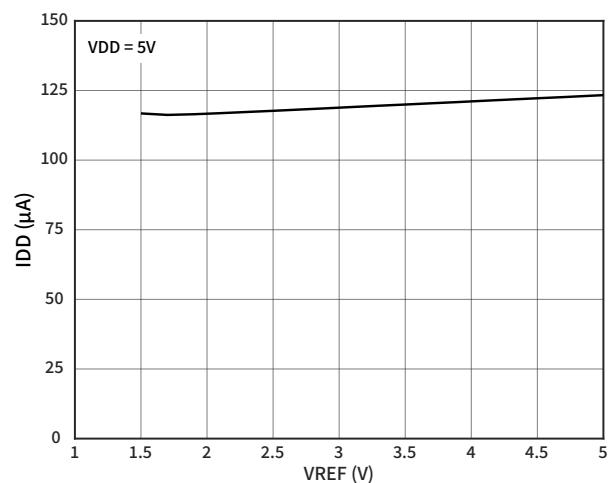

图 11 IDD 随 VREF 的变化 (VDD = 5V)

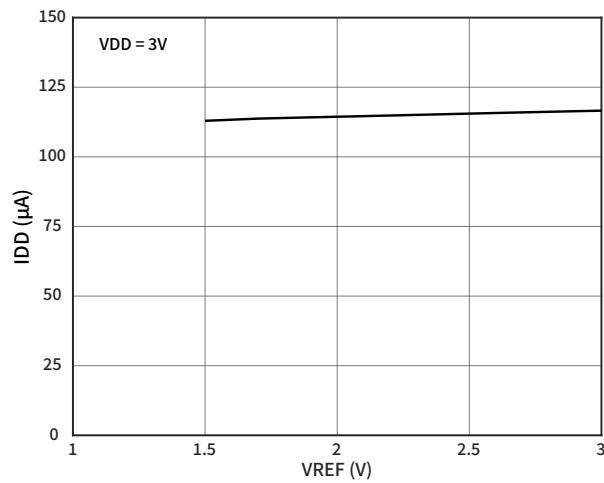

图 12 IDD 随 VREF 的变化 (VDD = 3V)

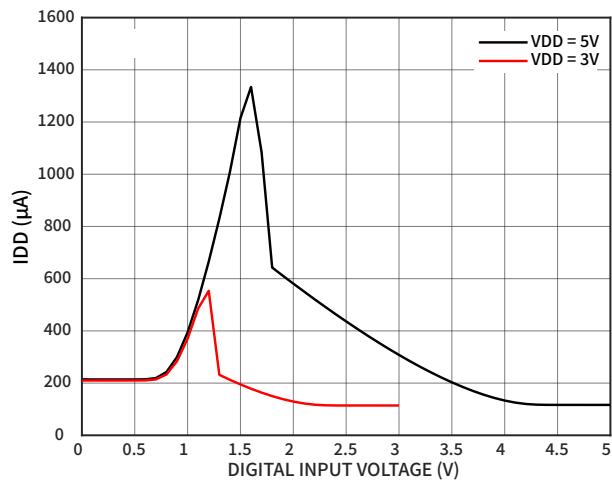

图 13 IDD 随 VIH 的变化

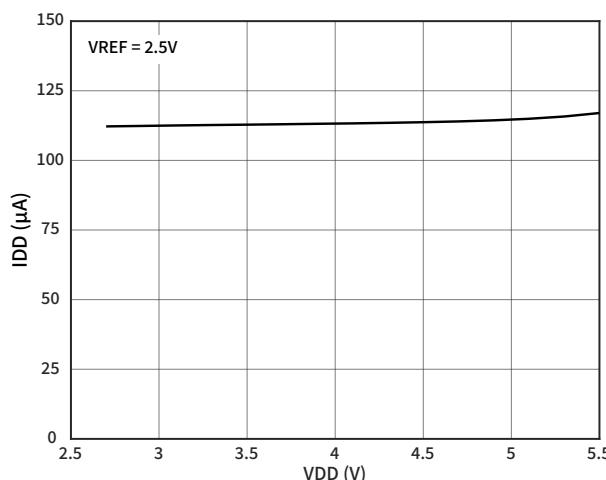

图 14 IDD 随 VDD 的变化

图 15 IDD 的温度特性

图 16 VOUT/VREF

图 17 数字馈通

图 18 主进位翻转毛刺脉冲

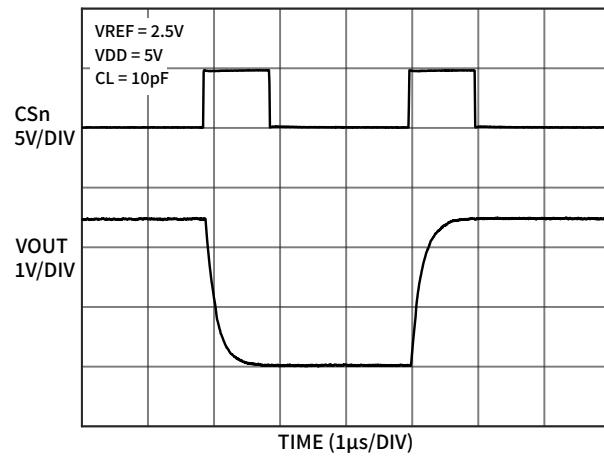

图 19 满量程高低电平转换

图 20 增益误差的温度特性

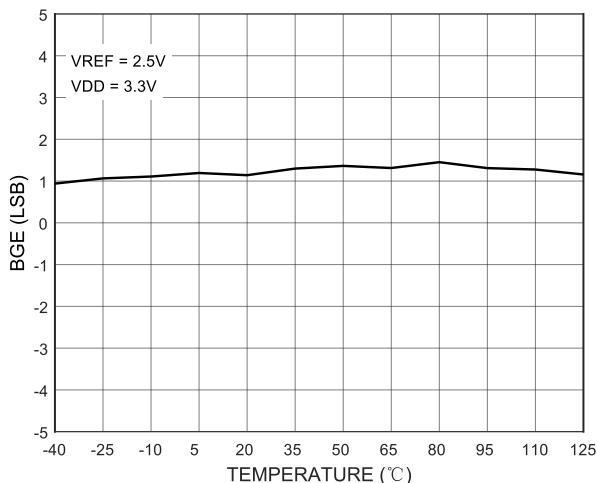

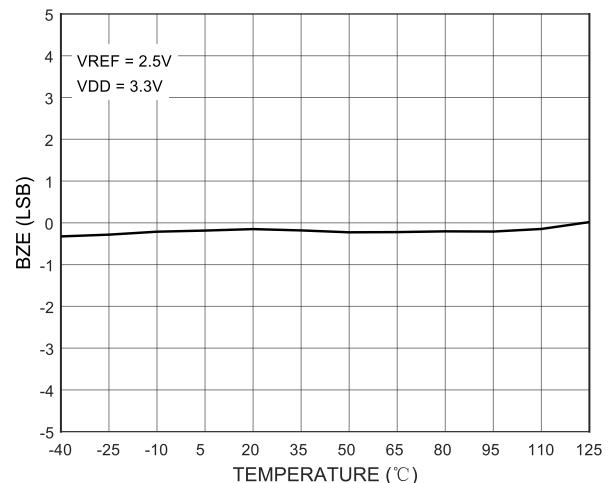

图 21 零码误差的温度特性

## 工作原理

CM7502L 是一款性能优越的 16 位 DAC，其 INL 和 DNL 均小于  $\pm 0.4$ LSB，可在全温范围内保证输出电压的单调性。CM7502L 采用单电源供电，电压范围为 2.7V 至 5.5V。同时支持 2V 至 VDD 的外部基准电压输入范围。内置 3 线串行接口可以便捷实现对 CM7502L 的相关配置。

## DAC 结构

DAC 结构为采用精准薄膜电阻和 CMOS 开关的梯形电阻网络。CM7502L 对电阻网络做了专门的分组。高四位输入码字经过解码后可控制 15 个相同的电阻支路，其余输入码字则控制低位的电阻支路。当负载电容设置为 10pF 时，主进位翻转产生的毛刺脉冲非常小，仅为 0.4nV·s，相较于同类型的 DAC 结构小了一个数量级。

CM7502L 采用数字校准算法，实现了超低的失调误差和满量程误差，以及超高的线性度。

VOUT 管脚的传递函数为：

$$VOUT = \left( \frac{k}{2^N} \right) VREF$$

其中  $k$  表示二进制 DAC 输入码字的十进制等价整数， $N$  表示分辨率，VREF 的范围为 2V 至 VDD。

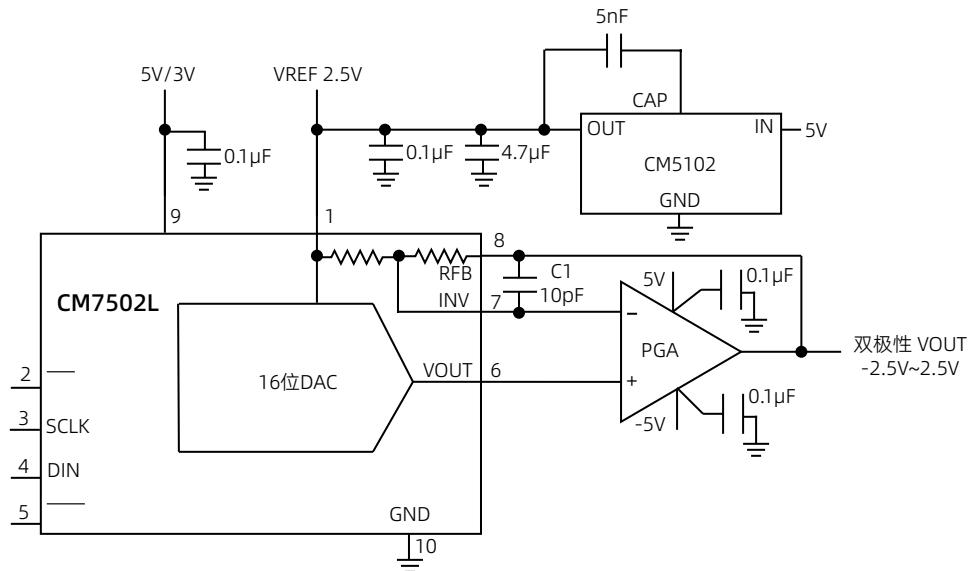

CM7502L 集成了一个精密匹配的电阻对，与一个外部放大器相连接，可以提供最大  $\pm VREF$  摆幅的双极性电压输出（参见图 1）。

RFB 管脚的双极性传递函数为（参见表 1）：

$$VOUT = VREF \left( \frac{k}{2^{N-1}} - 1 \right)$$

## 负载对 DAC 输出电压精度的影响

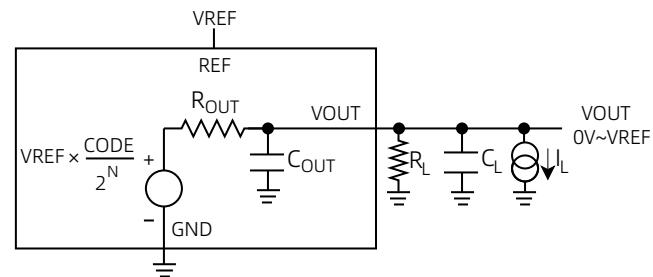

CM7502L 可直接通过 VOUT 管脚输出摆幅为 GND 至 VREF 的电压。片内无缓冲器的架构使得 DAC 可提供最低的失调、满量程和线性误差，同时获得最快的建立时间以及最低功耗。但是，无缓冲器的架构也限制了 DAC 输出级的驱动能力。CM7502L VOUT 可建模为理想电压源串联一个输出电阻  $R_{OUT}$ ， $R_{OUT}$  典型值为 6k $\Omega$ （参见图 22）。CM7502L 的线性输出阻抗在驱动中等负载 ( $R_L > 60k\Omega$ ) 时，仅增大增益误差，而不会使 INL 或 DNL 变差。负载电阻所引起的增益误差的计算公式为：

$$GE = \frac{-1}{\left( 1 + \frac{R_{OUT}}{R_L} \right)}$$

基于 LSB 的公式为：

$$GE = \frac{-65536}{\left( 1 + \frac{R_{OUT}}{R_L} \right)} [\text{LSB}]$$

其中  $R_{OUT}$  具有低温漂（典型值小于  $\pm 50\text{ppm}/^\circ\text{C}$ ），且与 DAC 输入码字无关。 $R_{OUT}$  的变化范围通常低于  $\pm 20\%$ 。

VOUT 的恒定负载电流  $I_L$  会产生一个如下失调电压：

$$V_{OFFSET} = -I_L \times R_{OUT}$$

对于 CM7502L，LSB 等于  $2 \times (2.5V/65536)$ ，即 76 $\mu\text{V}$ 。 $R_{OUT}$  等于 6k $\Omega$  时，6nA  $I_L$  会产生 1LSB 的失调电压。因此，为了避免 DAC 性能下降，需保证 VOUT 管脚免受任何漏电影响。

## 电压输出建立时间

VOUT 的建立时间可根据单极点响应进行近似估计，其中：

$$\tau = R_{OUT} \times (C_{OUT} + C_L)$$

DAC 输出电压精度建立到 1/2LSB 以内，大约需要  $\ln(2 \times 65536) \approx 12$  个时间常数。要保证 DAC VOUT 建立时间在 1 $\mu\text{s}$  以内，要求输出级  $C_{OUT}$  的时间常数小于 83ns，即负载电容小于  $83\text{ns}/6k = 13\text{pF}$ 。

图 22 VOUT 管脚等效电路

## 运算放大器

CM7502L 极小的 LSB 电压以及自身较高的精度，意味着外部运算放大器的选择对整个 DAC 性能非常关键。

外部缓冲运算放大器的选择取决于 DAC 是在双极性输出模式下还是单极性输出模式下工作，同时还受当前应用的精度、速度、功耗以及 PCB 板面积的影响。CM7502L 的微型封装、轨到轨单电源供电、低功耗、快速建立时间以及高精度等特点决定了同一款运算放大器很难适用于所有场景。

双极性输出模式下，运算放大器与片内电阻共同构成双极性输出环路，实现放大功能的同时，提供额外的失调电压。这种情形下，需要选用基于双电源工作的低失调精密放大器，以提供  $\pm VREF$  电压输出范围（参见图 1）。

单极性输出模式下，输出放大器作为单位增益电压跟随器运行。

## 运算放大器规格和 CM7502L 精度

大多数运算放大器的精度规格会直接影响 DAC 精度。

运算放大器同相 (+) 输入端的偏置电流相当于 VOUT 的恒定负载电流  $I_L$ ，因此会产生一个零码失调误差（参见 [负载对 DAC 输出电压精度的影响](#)）：

$$ZSE = -I_B(\text{IN}+) \times R_{OUT}$$

基于 LSB 的公式为：

$$ZSE = -I_B(IN+) \times 6k \times \frac{65536}{VREF} [LSB]$$

运算放大器的输入阻抗  $R_{IN}$  相当于  $V_{OUT}$  的负载  $R_L$ ，产生如下增益误差：

$$GE = \frac{-65536}{\left(1 + \frac{6k}{R_{IN}}\right)} [LSB]$$

运算放大器的失调电压  $V_{OS}$  相当于 DAC 零码失调误差  $ZSE$ ：

$$ZSE = V_{OS} \times \frac{65536}{VREF} [LSB]$$

同时还需要考虑温度因素。全温范围内，失调电压温漂（参考温度 25°C）为 0.6μV/°C 时，会增加 1LSB 的零码误差。此外， $I_{BIAS}$  与其产生的  $V_{OFFSET}$  误差也会随着温度呈现显著变化。

运算放大器开环增益  $A_{VOL}$  和 DAC 输出增益误差之间存在如下关系：

$$GE = \frac{65536}{A_{VOL}} [LSB]$$

运算放大器的共模抑制比 (CMRR) 会同时影响 DAC 输出的增益误差和 INL。选取的运算放大器架构以及应用中，实际运行的条件也会影响最终的输出误差。由 CMRR 引起的误差计算公式为：

$$\text{误差} = 10 \frac{CMRR}{20} \times \frac{V_{CMRR\_RANGE}}{VREF} \times 65536 [LSB]$$

其中， $V_{CMRR\_RANGE}$  表示指定的 CMRR 对应的共模电压输入范围。运算放大器的典型特征图可用于预测共模抑制比误差对 DAC 性能的影响。通常，一个精密运算放大器在共模电压输入范围的中段值 CMRR 指标的线性度更好（线性化的 CMRR 不会影响 DAC 的线性度）。当输入信号临近共模电压输入范围的边缘时，线性度会下降，体现出较大的非线性。

对于 CM7502L，DAC 的输出经过运算放大器环路放大，所有误差均增加到两倍。在运算放大器输出端 LSB 电压为 DAC 输出端的两倍。

双极性输出模式下，增加了一个  $I_B$  ( $IN-$ ) 误差， $I_B$  流经 RFB 产生一个失调电压。偏置电流失调误差公式为：

$$V_{OFFSET} = I_B(IN-) \times R_{FB} - I_B(IN+) \times R_{OUT} \times 2$$

因此：

$$V_{OFFSET} = \left( I_B(IN-) \times 28k - I_B(IN+) \times 12k \right) \times \frac{32768}{VREF} [LSB]$$

## 电压输出建立时间（使用运算放大器时）

使用外部运算放大器时，电压输出建立时间包括 CM7502L  $V_{OUT}$  节点上的单极点建立时间，时间常数的计算公式为  $R_{OUT} = (C_{OUT} + C_L)$ （参见 [电压输出建立时间](#)）。其中， $C_L$  包括放大器输入电容和 PCB 板的走线电容。

外部缓冲放大器会额外增加一个极点，时间常数等于带宽/2π。例如，假设  $C_L$  保持上述值， $V_{OUT}$  节点时间常数为 83ns（等于 1μs/12）。如果放大器闭环带宽为  $1/(2\pi \times 83ns) = 1.9MHz$ ，那么输出放大器也存在一个时间常数为 83ns 的极点。两个级联单极点部分的有效时间常数大约是各个时间常数的平方根之和或  $\sqrt{2} \times 83ns = 117ns$ ，因此  $1/2LSB$  建立时间为  $\approx 12 \times 117ns = 1.4\mu s$ 。这只是一个理想情况，不考虑摆幅限制和运算放大器相位裕度。实际上需要选用带宽较大的放大器，并保持足够的相位裕度，才能接近 1μs 的无缓冲建立时间。

电压输出建立时间（参见 [电压输出建立时间](#)）会因反馈电阻  $R_{FB}$  和  $R_{INV}$ （典型值均为 28kΩ）有所增加。运算放大器反相输入端 (-) 上的寄生电容  $C_p$  会引入一个时间常数为  $(C_p \times 28k\Omega/2)$  的反馈环路极点。同时，在反馈环路上应包括一个小的反馈电容  $C_1$ ，引入一个零压来抵消该极点。 $C_1$  典型值应小于  $C_p$ ，通常在 5pF 至 10pF 之间。引入  $C_1$  后可以提升相位裕度，并减小建立时间。但是零极点必然导致建立时间变慢，时间常数大约为  $(C_p + C_1) \times 28k\Omega/2$ ，会使得建立时间大于 2μs。

## 电压基准

CM7502L 采用范围为 2V 至 VDD 的外部电压基准进行工作，其本身的线性度、失调误差和增益误差几乎不受基准电压的影响。CM7502L 的较低增益误差温漂 0.2ppm/°C（典型值）相当于全温范围内低于 1/2LSB 的变化。实际上，这意味着总体增益误差温漂几乎全部由外部基准温漂决定。

为了防止梯形电阻网络分支从 GND 到  $VREF$  转换时产生输出毛刺，电压基准在高频下必须保持较低输出阻抗。表贴陶瓷电容具有最低的寄生电感，在尽可能靠近 CM7502L REF 和 GND 管脚之间的位置摆放一个 0.1μF 的陶瓷电容，以提供高频旁路。如果空间允许，REF 和 GND 之间可额外再添加 1μF 的陶瓷电容，作为低频旁路电容。只要外部电压基准可以在增加电容负载时仍保持稳定，CM7502L 就会受益于更大的旁路电容。

## 复位

CM7502L 内置上电复位电路，确保输出状态可控。当给 VDD 上电后，CM7502L 上电复位至双极性输出中间电平。根据其位数，中间电平码字为 32768。

异步  $\overline{CLR}$  低脉冲也可将 CM7502L 输出复位至中间电平。

## 数字接口

### 串行接口

CM7502L 通过 3 线 SPI/QSPI/MICROWIRE 兼容接口进行通信。 $\overline{CS}$  控制来自 DIN 串行数据的加载。当  $\overline{CS}$  为低电平时，DIN 数据被 16 个 SCLK 的上升沿加载到移位寄存器（MSB 优先）。如果 SCLK 的上升沿数量少于 16 个，数据将无效，需要重新加载。如果 SCLK 的上升沿数量多于 16 个，仅 DIN 最先加载的 16 数据位会被传输至 DAC 锁存器。16 位数据被加载完成后， $\overline{CS}$  上升沿将数据锁存至 16 位 DAC 锁存器，并更新 DAC 输出电压（参见图 23）。当  $\overline{CS}$  为高电平时，串行输入移位寄存器被禁用。

### 数字输入和接口逻辑

所有数字输入均含有施密特缓冲器，以兼容慢速转换接口。因此，光耦合器可直连 CM7502L，无需额外的逻辑器件。迟滞电压典型值为 180mV。

数字输入与 TTL/CMOS 逻辑电平兼容，但更倾向于使用达到电源轨摆幅的 CMOS 逻辑，以避免产生额外的 IDD 和 GND 电流。

数字馈通的典型值只有  $0.2\text{nV}\cdot\text{s}$ ，但是除了 DAC 更新输入之外，仍要尽量保证所有的逻辑输入不翻转。

图 23 时序图

## 应用

图 24 显示了 CM7502L 的典型应用连接。片上失调/增益电阻 RFB 和 RINV 连接至一个外部放大器，在 RFB 管脚产生 -VREF 至 VREF 的输出摆幅。放大器电路从 VOUT 管脚提供 +2 增益，从 VREF 提供 -1 增益。表 1 显示了双极性二进制码。

表 1 双极性二进制码

| 二进制码 |      |      |      | 模拟输出 (VOUT)        |

|------|------|------|------|--------------------|

| MSB  |      | LSB  |      |                    |

| 1111 | 1111 | 1111 | 1111 | VREF (32767/32768) |

| 1000 | 0000 | 0000 | 0001 | VREF (1/32768)     |

| 1000 | 0000 | 0000 | 0000 | 0V                 |

| 0111 | 1111 | 1111 | 1111 | -VREF (1/32768)    |

| 0000 | 0000 | 0000 | 0000 | -VREF              |

图 24 典型连接

## 封装及订购信息

### 封装方式

CM7502L 采用 MSOP10 和 DFN10 封装。

### 产品外形图

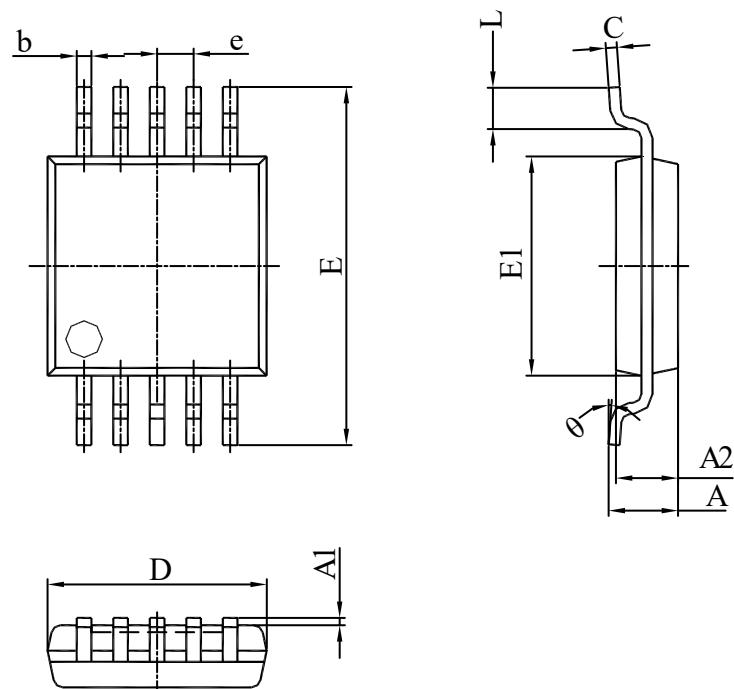

#### MSOP10

| 标识 | 尺寸 (毫米)    |      |      |

|----|------------|------|------|

|    | 最小值        | 典型值  | 最大值  |

| A  | -          | -    | 1.10 |

| A1 | 0.02       | 0.09 | 0.15 |

| A2 | 0.75       | 0.85 | 0.95 |

| b  | 0.18       | 0.26 | 0.33 |

| c  | 0.09       | 0.16 | 0.23 |

| D  | 2.90       | 3.00 | 3.10 |

| e  | 0.50 (BSC) |      |      |

| E  | 4.75       | 4.90 | 5.05 |

| E1 | 2.90       | 3.00 | 3.10 |

| L  | 0.40       | 0.60 | 0.80 |

| θ  | 0°         | 3°   | 6°   |

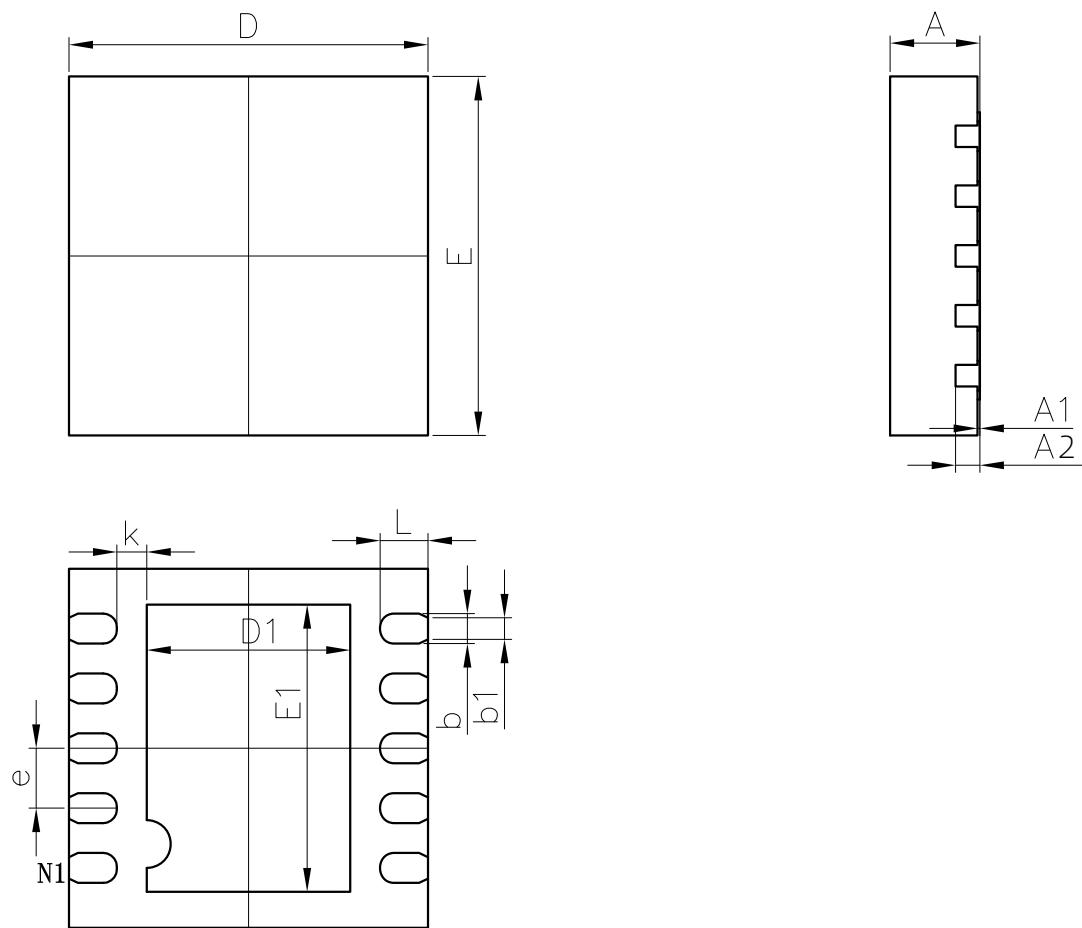

## DFN10

| Mark | Dimensions (mm) |      |      |

|------|-----------------|------|------|

|      | Min             | Typ  | max  |

| A    | 0.70            | 0.75 | 0.80 |

| A1   | 0               | 0.03 | 0.05 |

| A2   | 0.20 (REF)      |      |      |

| D    | 2.92            | 3.00 | 3.08 |

| E    | 2.92            | 3.00 | 3.08 |

| D1   | 1.60            | 1.70 | 1.80 |

| E1   | 2.30            | 2.40 | 2.50 |

| b    | 0.20            | 0.25 | 0.30 |

| b1   | 0.18 (REF)      |      |      |

| e    | 0.50 (BSC)      |      |      |

| k    | 0.25 (REF)      |      |      |

| L    | 0.32            | 0.40 | 0.48 |

## 订购信息

| 型号            | 温度范围        | 封装     | 包装   | 包装数量 |

|---------------|-------------|--------|------|------|

| CM7502L-MSOTA | -40°C~125°C | MSOP10 | Reel | 4000 |

| CM7502L-DFNTA | -40°C~125°C | DFN10  | Reel | 5000 |