## 特征

- 双通道同步采样

- 支持全差分输入

- 采样率：2MSPS

- INL:  $\pm 1\text{LSB}$

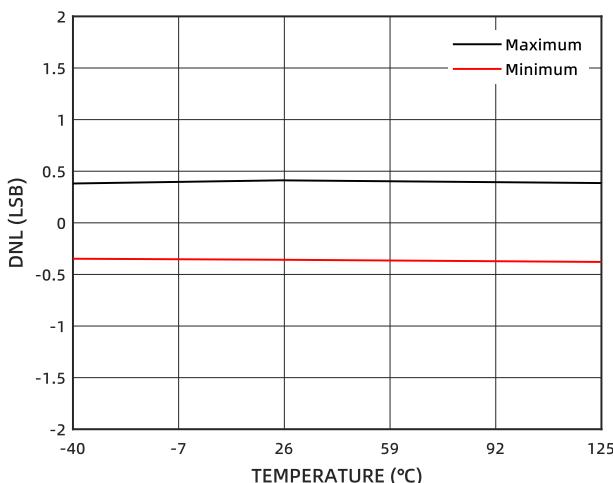

- DNL:  $\pm 0.4\text{LSB}$

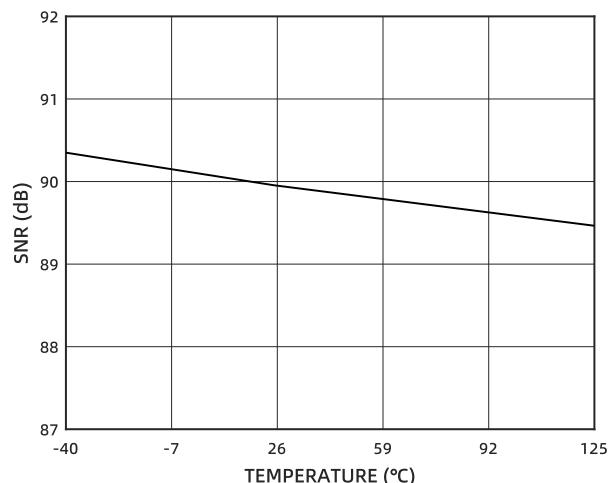

- SNR: 典型值为 90.4dB

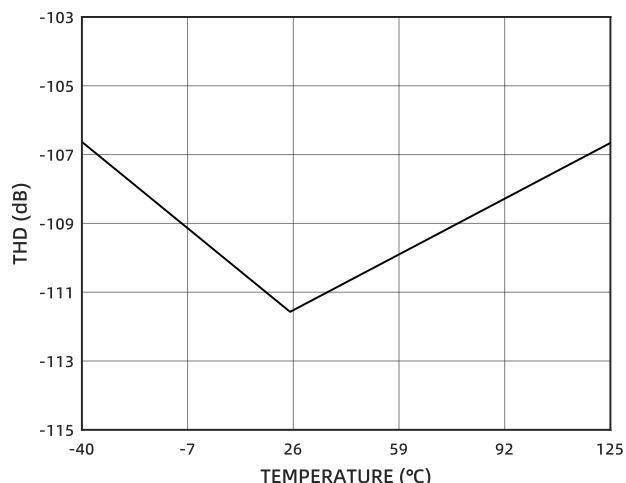

- THD: 典型值为 -108dB ( $\pm V_{REF}$  输入范围)

- 双路、2.5V 内部基准电压

- 通道隔离度: 典型值为 -122dB

- VDD 电流: 典型值为 20mA

- QFN16 3mm × 3mm 封装

## 应用

- 电机控制: 使用编码器进行位置测量

- 光纤网络: 捷联光纤放大器 (EDFA) 增益控制环路

- 保护继电器

- 电源质量测量

- 三相电源控制

- 可编程逻辑控制器

## 概述

CM2272 是一款 16 位、高速、双通道同步采样 SAR ADC，支持全差分模拟输入。

CM2272 支持宽模拟电源电压范围，每个通道均包含一个基准源；同时配备灵活的串行接口，支持多种数据读取模式。

CM2272 采用 QFN16 型封装，其额定工作温度范围为  $-40^\circ\text{C} \sim 125^\circ\text{C}$ 。

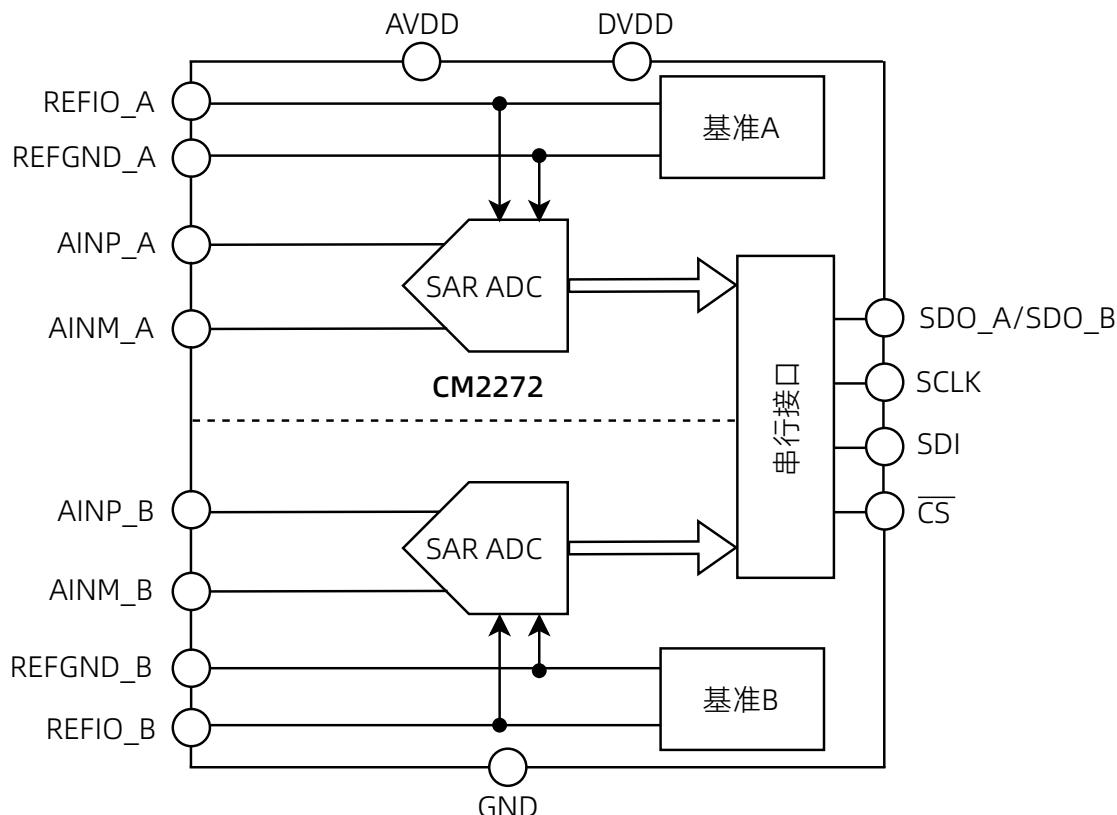

## 架构框图

# 目录

|              |    |                      |    |

|--------------|----|----------------------|----|

| 封页.....      | 1  | 共模电压范围.....          | 12 |

| 特征.....      | 1  | 抗混叠滤波器.....          | 13 |

| 应用.....      | 1  | ADC 传递函数.....        | 14 |

| 概述.....      | 1  | 数字接口.....            | 15 |

| 架构框图.....    | 1  | 读取转换结果.....          | 15 |

| 文档历史.....    | 3  | 32-SCK SDO 输出模式..... | 15 |

| 管脚配置和功能..... | 4  | 16-SCK SDO 输出模式..... | 16 |

| 管脚配置.....    | 4  | 读寄存器数据.....          | 17 |

| 管脚功能.....    | 4  | 写寄存器数据.....          | 17 |

| 绝对最大额定值..... | 5  | 寄存器.....             | 19 |

| 电气规格.....    | 6  | 配置寄存器 (CONFIG).....  | 19 |

| 时序规格.....    | 8  | DEVICE ID 寄存器.....   | 19 |

| 典型特征.....    | 10 | 封装及订购信息.....         | 20 |

| 工作原理.....    | 12 | 封装方式.....            | 20 |

| 内部基准.....    | 12 | 产品外形图.....           | 20 |

| 模拟输入.....    | 12 | 订购信息.....            | 21 |

| 满量程范围.....   | 12 |                      |    |

## 文档历史

下表列举了本文档自产品发布后的所有更新。

| 文档版本 | 修订日期       | 内容描述                                                                                                            |

|------|------------|-----------------------------------------------------------------------------------------------------------------|

| V0.1 | 2025-08-26 | 预发布。                                                                                                            |

| V0.5 | 2025-09-23 | <ul style="list-style-type: none"><li>根据实验室数据更新<a href="#">电气规格</a>。</li><li>新增<a href="#">典型特征图</a>。</li></ul> |

## 管脚配置和功能

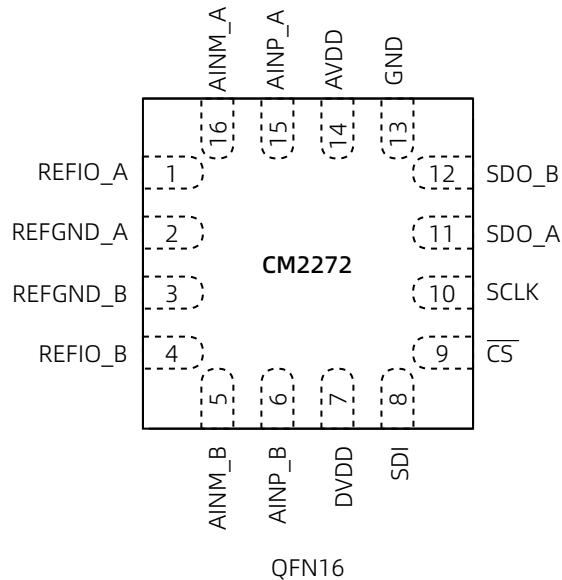

### 管脚配置

以下为 CM2272 QFN16 封装管脚示意图：

### 管脚功能

| 编号 | 名称       | 类型  | 说明           |

|----|----------|-----|--------------|

| 1  | REFIO_A  | AO  | 通道 A 基准电压输出。 |

| 2  | REFGND_A | PWR | 通道 A 参考地。    |

| 3  | REFGND_B | PWR | 通道 B 参考地。    |

| 4  | REFIO_B  | AO  | 通道 B 基准电压输出。 |

| 5  | AINM_B   | AI  | 通道 B 模拟负端输入。 |

| 6  | AINP_B   | AI  | 通道 B 模拟正端输入。 |

| 7  | DVDD     | PWR | 数字 IO 电源。    |

| 8  | SDI      | DI  | 串行数据输入。      |

| 9  | CS       | DI  | 片选。低电平有效。    |

| 10 | SCLK     | DI  | 串行时钟输入。      |

| 11 | SDO_A    | DO  | 通道 A 串行数据输出。 |

| 12 | SDO_B    | DO  | 通道 B 串行数据输出。 |

| 13 | GND      | GND | 地。           |

| 14 | AVDD     | PWR | ADC 工作电源。    |

| 15 | AINP_A   | AI  | 通道 A 模拟正端输入。 |

| 16 | AINM_A   | AI  | 通道 A 模拟负端输入。 |

## 绝对最大额定值

| 参数                                       | 等级                              |

|------------------------------------------|---------------------------------|

| <b>温度</b>                                |                                 |

| 工作温度                                     | -40°C~125°C                     |

| 存储温度                                     | 150°C                           |

| 结温                                       | -65°C~150°C                     |

| <b>耐压</b>                                |                                 |

| AVDD 至 REFGND_X                          | -0.3V~6V                        |

| DVDD 至 GND                               | -0.3V~6V                        |

| AINP_X/AINM_X 与 REFIO_X 相对于 REFGND_X 的电压 | (REFGND_X - 0.3)V~(AVDD + 0.3)V |

| 数字输入电压相对于 GND 的电压                        | (GND - 0.3)V~(DVDD + 0.3)V      |

| 地电压差(REFGND_X - GND)                     | 0.3V                            |

| 非电源管脚的输入电流                               | ±10mA                           |

## 电气规格

默认测试条件: AVDD = 5V, DVDD = 3.3V, VREF\_A = VREF\_B = VREF = 2.5V (内部基准电压), f<sub>DATA</sub> = 2MSPS, TA = -40°C~125°C。

| 参数                                | 测试条件                                                             | 最小值       | 典型值      | 最大值 | 单位     |

|-----------------------------------|------------------------------------------------------------------|-----------|----------|-----|--------|

| <b>直流精度</b>                       |                                                                  |           |          |     |        |

| 分辨率                               | 无失码                                                              | 16        |          |     | Bits   |

| INL                               |                                                                  | ±1        |          |     | LSB    |

| DNL                               |                                                                  | ±0.4      |          |     | LSB    |

| 输入失调误差                            |                                                                  | ±0.3      |          |     | mV     |

| 输入失调误差匹配                          |                                                                  | 0.3       |          |     | mV     |

| 输入失调误差温漂                          |                                                                  | ±0.6      |          |     | µV/°C  |

| 增益误差                              | 参考 REFIO_X 电压                                                    | ±0.025    |          |     | %FS    |

| 增益误差匹配                            |                                                                  | 0.003     |          |     | %FS    |

| 增益误差温漂                            | 参考 REFIO_X 电压                                                    | ±1.4      |          |     | ppm/°C |

| <b>动态性能</b>                       |                                                                  |           |          |     |        |

| SNR                               | VREF = 2.5V, ±VREF 输入范围                                          | 90        |          |     | dB     |

|                                   | VREF = 2.5V, ±2 × VREF 输入范围                                      | 90.4      |          |     | dB     |

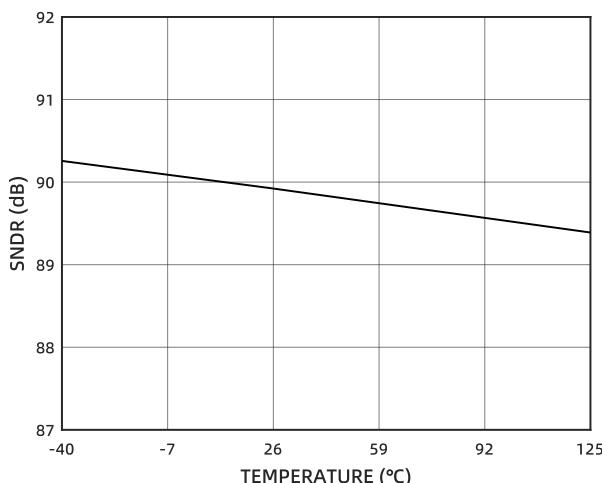

| SNDR                              | VREF = 2.5V, ±VREF 输入范围                                          | 89.8      |          |     | dB     |

|                                   | VREF = 2.5V, ±2 × VREF 输入范围                                      | 90.2      |          |     | dB     |

| THD                               | VREF = 2.5V, ±VREF 输入范围                                          | -108      |          |     | dB     |

|                                   | VREF = 2.5V, ±2 × VREF 输入范围                                      | -106      |          |     | dB     |

| SFDR                              | VREF = 2.5V, ±VREF 输入范围                                          | 110       |          |     | dB     |

|                                   | VREF = 2.5V, ±2 × VREF 输入范围                                      | 108       |          |     | dB     |

| 通道隔离度                             | f <sub>IN</sub> = 15kHz (10%FS), f <sub>NOISE</sub> = 25kHz (FS) |           | -122     |     | dB     |

| CMRR                              | 直流到 20kHz                                                        | 83        |          |     | dB     |

| 孔径延迟                              |                                                                  | 2         |          |     | ns     |

| 孔径延迟匹配                            |                                                                  | 40        |          |     | ps     |

| 孔径抖动                              |                                                                  | 50        |          |     | ps     |

| <b>模拟输入</b>                       |                                                                  |           |          |     |        |

| 全量程输入范围 (AINP_X - AINM_X)         | ±VREF 范围                                                         | -VREF     | VREF     |     | V      |

|                                   | ±VREF 范围, AVDD = 3.3V                                            | -VREF     | VREF     |     | V      |

|                                   | ±2 × VREF 范围, AVDD ≥ 2 × VREF                                    | -2 × VREF | 2 × VREF |     | V      |

| 绝对输入电压 (AINP_X / AINM_X 到 REFGND) | ±VREF 范围                                                         | 0         | VREF     |     | V      |

|                                   | ±VREF 范围, AVDD = 3.3V                                            | 0         | VREF     |     | V      |

|                                   | ±2 × VREF 范围, AVDD ≥ 2 × VREF                                    | 0         | 2 × VREF |     | V      |

| 参数                                           | 测试条件                                                                         | 最小值                        | 典型值                | 最大值                        | 单位                      |

|----------------------------------------------|------------------------------------------------------------------------------|----------------------------|--------------------|----------------------------|-------------------------|

| 共模电压范围( $\text{AINP}_X + \text{AINM}_X)/2$   | $\pm V_{\text{REF}}$ 范围                                                      | $(V_{\text{REF}}/2) - 0.1$ | $V_{\text{REF}}/2$ | $(V_{\text{REF}}/2) + 0.1$ | V                       |

|                                              | $\pm V_{\text{REF}}$ 范围, $\text{AVDD} = 3.3\text{V}$                         | $(V_{\text{REF}}/2) - 0.1$ | $V_{\text{REF}}/2$ | $(V_{\text{REF}}/2) + 0.1$ | V                       |

|                                              | $\pm 2 \times V_{\text{REF}}$ 范围, $\text{AVDD} \geq 2 \times V_{\text{REF}}$ | $V_{\text{REF}} - 0.1$     | $V_{\text{REF}}$   | $V_{\text{REF}} + 0.1$     | V                       |

| 输入电容                                         | 采样模式                                                                         |                            | 14                 |                            | pF                      |

|                                              | 保持模式                                                                         |                            | 4                  |                            | pF                      |

| 输入漏电流                                        |                                                                              |                            | 0.1                |                            | $\mu\text{A}$           |

| <b>基准输入/输出</b>                               |                                                                              |                            |                    |                            |                         |

| 基准输出电压                                       |                                                                              | 2.495                      | 2.5                | 2.505                      | V                       |

| $V_{\text{REF\_A}}$ 到 $V_{\text{REF\_B}}$ 匹配 |                                                                              |                            | $\pm 0.5$          |                            | mV                      |

| 基准电压温漂                                       |                                                                              |                            | $\pm 10$           |                            | ppm/ $^{\circ}\text{C}$ |

| 长期漂移                                         | 1000 小时                                                                      |                            | 150                |                            | ppm/1000 hours          |

| 内部基准输出阻抗                                     |                                                                              |                            | 1                  |                            | $\Omega$                |

| 基准输出直流电流                                     |                                                                              |                            | 2                  |                            | mA                      |

| 建议输出电容                                       | $C_{\text{REF}} = 10\mu\text{F}$                                             |                            | 10                 |                            | $\mu\text{F}$           |

| 基准输出建立时间                                     |                                                                              |                            | 8                  |                            | ms                      |

| <b>数字输入/输出</b>                               |                                                                              |                            |                    |                            |                         |

| $V_{\text{IH}}$                              |                                                                              | 0.7 DVDD                   |                    | DVDD + 0.3                 | V                       |

| $V_{\text{IL}}$                              |                                                                              | -0.3                       |                    | 0.3 DVDD                   | V                       |

| 输入电流                                         |                                                                              |                            | $\pm 10$           |                            | nA                      |

| $V_{\text{OH}}$                              | $I_{\text{SOURCE}} = 500\mu\text{A}$                                         | 0.8 DVDD                   |                    | DVDD                       | V                       |

| $V_{\text{OL}}$                              | $I_{\text{SINK}} = 500\mu\text{A}$                                           | 0                          |                    | 0.2 DVDD                   | V                       |

| <b>电源功耗</b>                                  |                                                                              |                            |                    |                            |                         |

| AVDD                                         | $\pm V_{\text{REF}}$ 范围                                                      | 3                          | 5                  | 5.5                        | V                       |

|                                              | $\pm 2 \times V_{\text{REF}}$ 范围                                             | 5                          | 5                  | 5.5                        | V                       |

| DVDD                                         |                                                                              |                            | 3.3                |                            | V                       |

| AIDD                                         | 快速吞吐                                                                         |                            | 20                 |                            | mA                      |

| 功耗                                           | 快速吞吐                                                                         |                            | 102.5              |                            | mW                      |

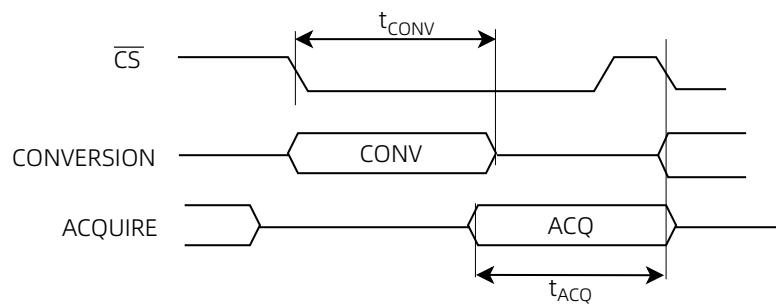

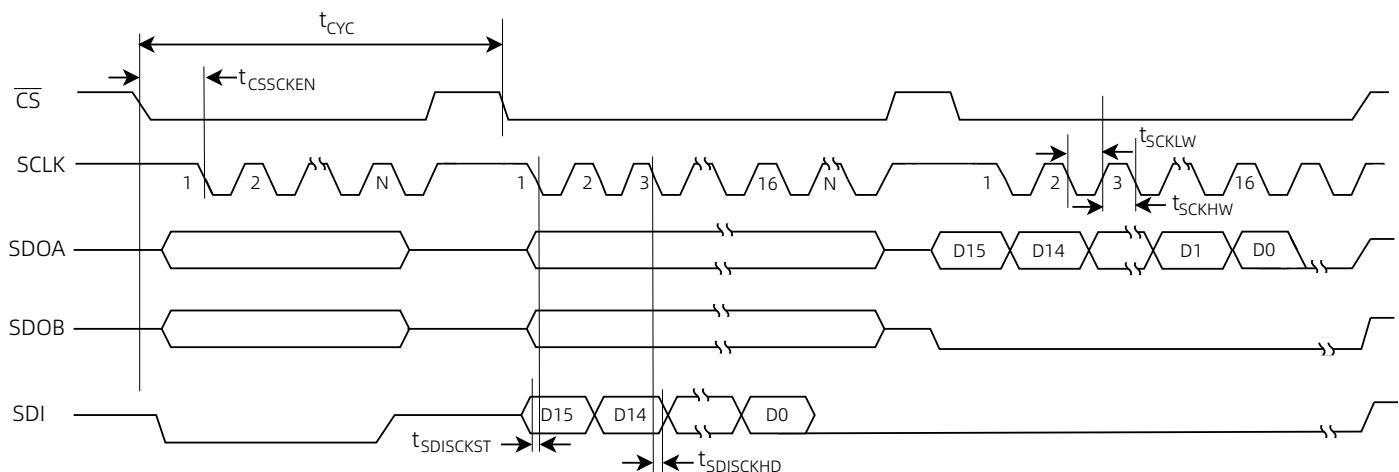

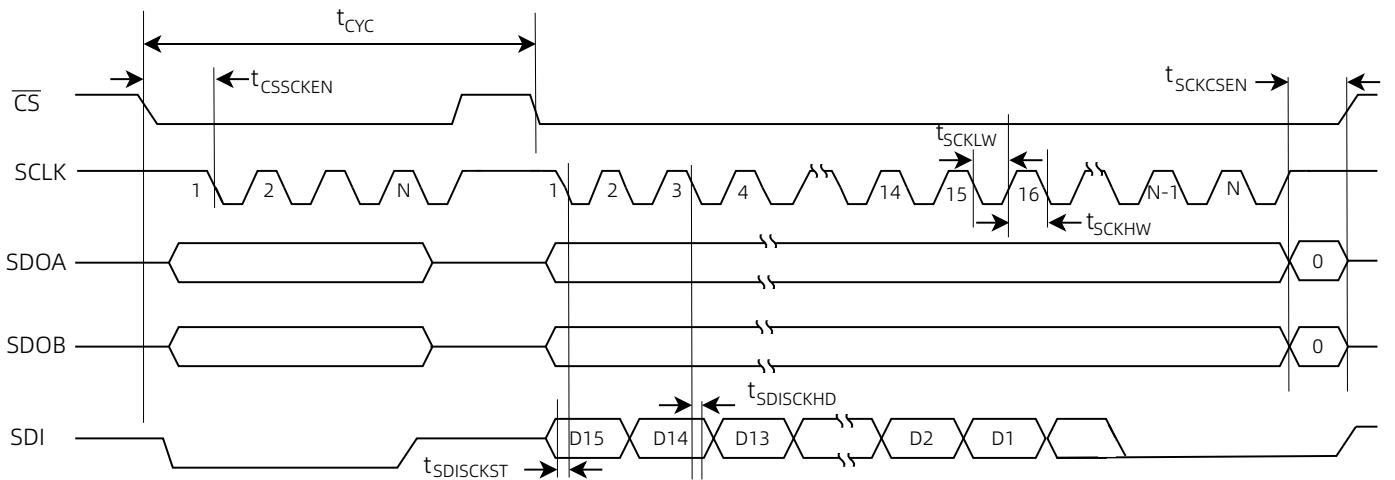

## 时序规格

| 参数                    | 描述                                       | 最小值 | 典型值 | 最大值  | 单位 |

|-----------------------|------------------------------------------|-----|-----|------|----|

| t <sub>CYC</sub>      | 转换周期                                     | 500 |     |      | ns |

| t <sub>CSSCKEN</sub>  | $\overline{CS}$ 下降沿到第一个 SCLK 下降沿之间的时间间隔  | 14  |     |      | ns |

| t <sub>SCK</sub>      | SCLK 周期                                  | 14  |     |      | ns |

| t <sub>SCKHW</sub>    | SCLK 高电平脉冲宽度                             |     | 7   |      | ns |

| t <sub>SCLLW</sub>    | SCLK 低电平脉冲宽度                             |     | 7   |      | ns |

| t <sub>CSW</sub>      | $\overline{CS}$ 脉冲宽度                     | 15  |     |      | ns |

| t <sub>CSSDOST</sub>  | $\overline{CS}$ 下降沿到 SDO 数据有效建立时间        | 7.3 |     | 14   | ns |

| t <sub>CSSDOHD</sub>  | SCLK 上升沿到 SDO 依然有效保持时间                   | 3   |     |      | ns |

| t <sub>SCKSDOST</sub> | SCLK 上升沿到 SDO 有效建立时间                     |     |     | 13.7 | ns |

| t <sub>CSSDOH</sub>   | $\overline{CS}$ 上升沿到 SDO 变为高阻态时间         |     |     | 6    | ns |

| t <sub>SDISCKST</sub> | SDI 有效到 SCLK 下降沿建立时间                     | 3   |     |      | ns |

| t <sub>SDISCKHD</sub> | SDI 有效到 SCLK 下降沿保持时间                     | 3   |     |      | ns |

| t <sub>SCKCSEN</sub>  | SCLK 最后一个上升沿到 $\overline{CS}$ 上升沿之间的时间间隔 | 0   |     |      | ns |

| t <sub>CONV</sub>     | 转换时间                                     | 295 |     |      | ns |

| t <sub>ACQ</sub>      | 采样时间                                     |     |     | 275  | ns |

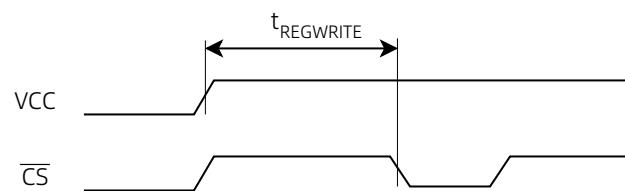

| t <sub>POWERUP</sub>  | 上电后开始第一次转换时间                             |     |     | 5    | ms |

| t <sub>REGWRITE</sub> | 上电后寄存器读写访问时间                             |     |     | 5    | ms |

| t <sub>QUIET1</sub>   | 转换启动后, 为保证最佳性能, SPI 接口静默时间               | 220 |     |      | ns |

| t <sub>QUIET2</sub>   | 转换启动前, 为保证最佳性能, SPI 接口静默时间               | 10  |     |      | ns |

图 1 内部转换采集时序

图 2 上电到开始转换的时间间隔

## 典型特征

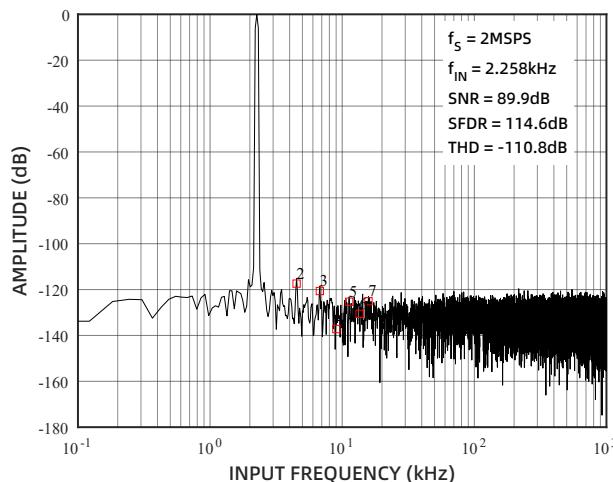

图 3 FFT

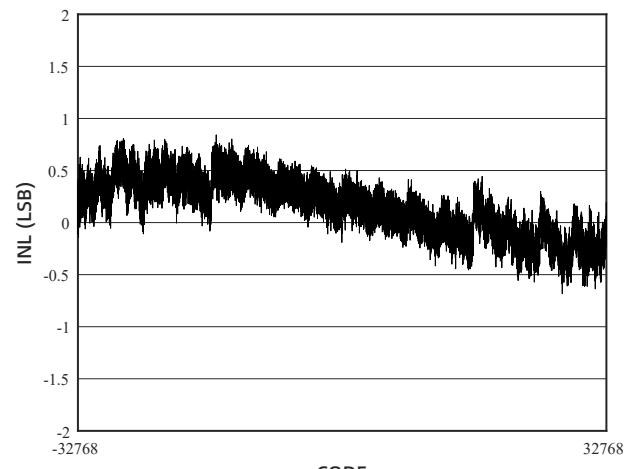

图 4 INL

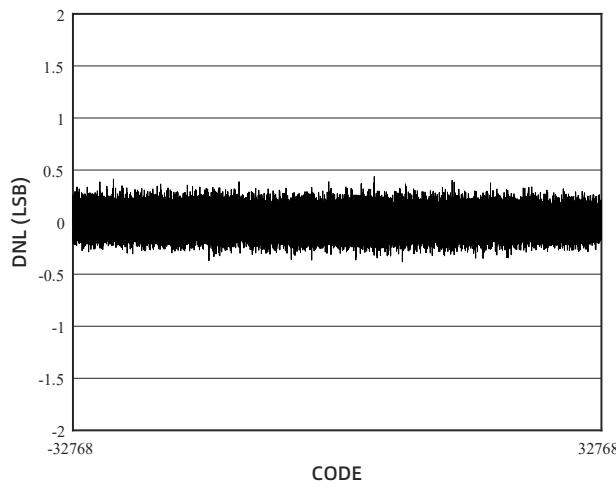

图 5 DNL

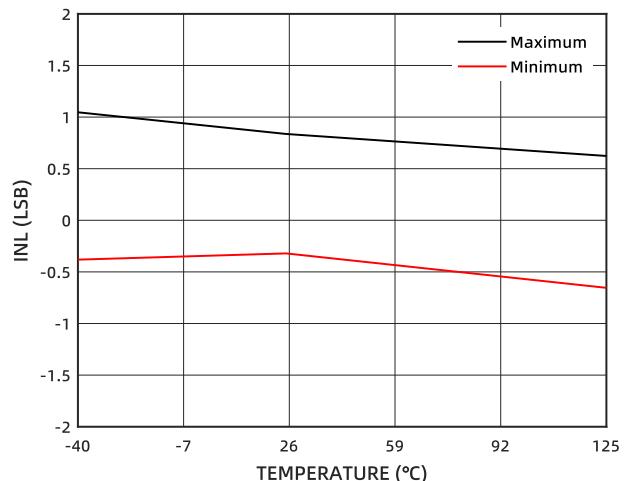

图 6 INL 的温度特性

图 7 DNL 的温度特性

图 8 SNR 的温度特性

图 9 SNDR 的温度特性

图 10 THD 的温度特性

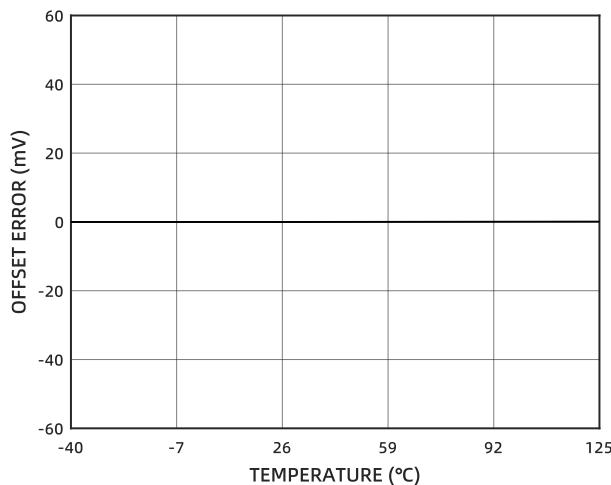

图 11 输入失调误差的温度特性

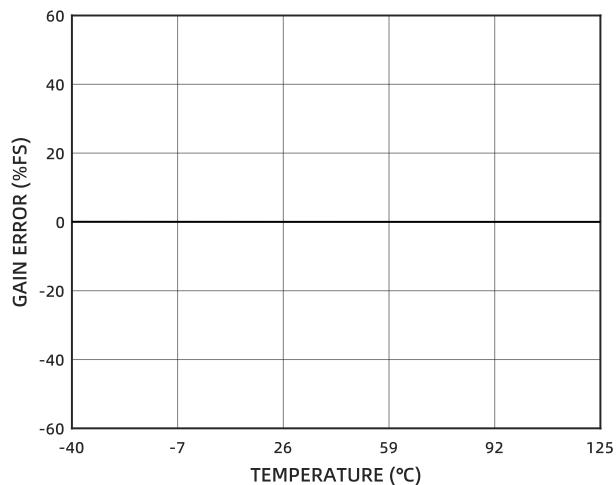

图 12 增益误差的温度特性

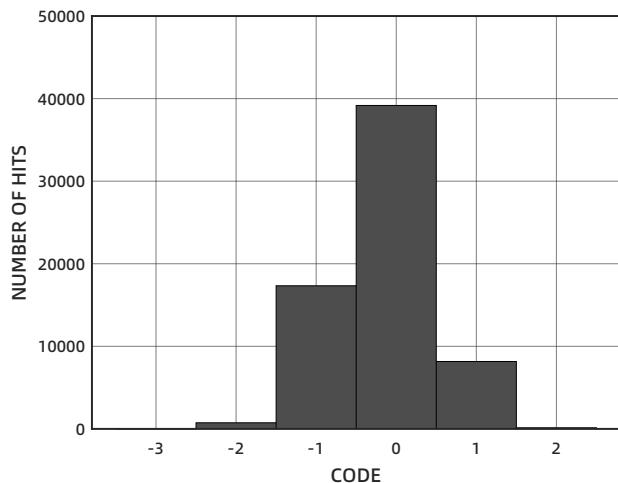

图 13 零输入直方图

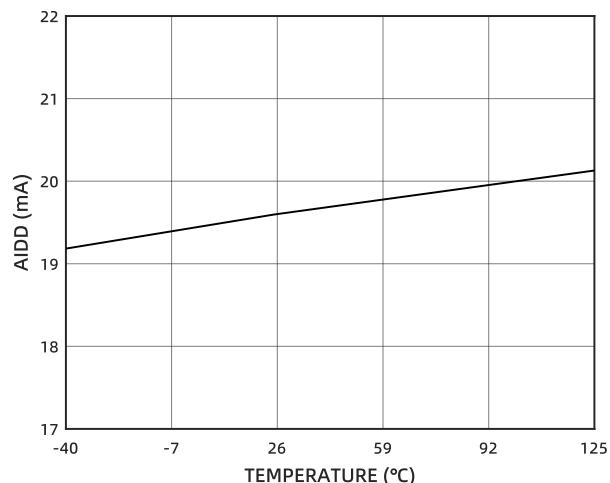

图 14 VDD 电流

## 工作原理

CM2272 是一款 16 位、高速、双通道同步采样 SAR ADC，支持全差分模拟输入。其提供简化的串行接口，可高效与主控制器通信，并支持在较宽的模拟电源电压范围内稳定工作。

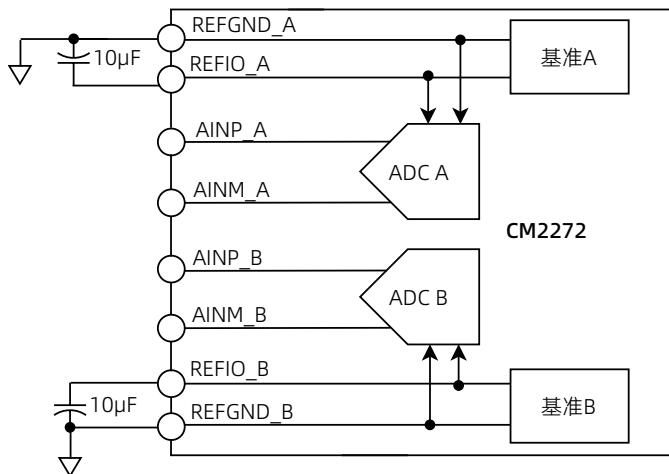

## 内部基准

CM2272 集成了两个独立的同步采样 ADC (ADC A 和 ADCB)，采用双基准电压架构，分别为两个转换通道提供独立的基准电压源 VREF\_A 和 VREF\_B。在电源设计方面，每个基准电压管脚 (REFIO\_A 和 REFIO\_B) 需外接 10μF 去耦电容，并连接至对应的基准地 (REFGND\_A 和 REFGND\_B)。

图 15 基准电压电路

## 模拟输入

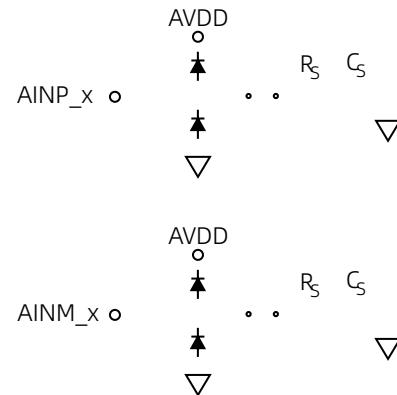

CM2272 支持全差分模拟输入。其片内集成的两个独立模数转换器 ADC A 和 ADC B 可对输入信号进行同步采样与转换：ADC A 负责对差分输入信号( $V_{AINP\_A} - V_{AINM\_A}$ ) 进行采样与转换，ADC B 则同步处理( $V_{AINP\_B} - V_{AINM\_B}$ )差分信号。

图 16 展示了 ADC A 与 ADC B 模拟输入管脚的等效电路结构。该电路包含一个串联电阻  $R_S$ ，代表采样开关处于导通状态时的导通电阻（典型值为 50Ω），以及一个片内采样电容  $C_S$ （典型值为 14pF）。

图 16 等效模拟输入电路

## 满量程范围

CM2272 的模拟输入支持可编程满量程范围 (FSR)，通过配置寄存器的 B9 位(INPUT\_RANGE)统一控制 ADC A 和 ADC B 的量程设置。具体量程范围由以下公式定义：

当 INPUT\_RANGE = 0 时：

$$FSR_{ADC\_A} = \pm V_{REF\_A}, FSR_{ADC\_B} = \pm V_{REF\_B}.$$

当 INPUT\_RANGE = 1 时：

$$FSR_{ADC\_A} = \pm 2 \times V_{REF\_A}, FSR_{ADC\_B} = \pm 2 \times V_{REF\_B}.$$

其中， $V_{REF\_A}$  和  $V_{REF\_B}$  分别指 ADC A 和 ADC B 的基准电压。

## 需要注意事项：

当 INPUT\_RANGE 设置为 1 时，必须确保 ADC 模拟电源(AVDD)满足以下条件：

$$2 \times V_{REF\_A} \leq AVDD \leq AVDD \text{ (最大值)}$$

$$2 \times V_{REF\_B} \leq AVDD \leq AVDD \text{ (最大值)}$$

## 共模电压范围

CM2272 支持多种差分输入配置，其共模电压范围由以下公式定义：

$$V_{CM\_A} = FSR_{ADC\_A}/2$$

$$V_{CM\_B} = FSR_{ADC\_B}/2$$

CM2272 支持的不同输入配置如下：

| 输入范围选择                                                                                                  | 输入共模范围                                                                                                                       | 连线图 |

|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| INPUT_RANGE<br>(FSR_ADC A = $\pm V_{REF\_A}$ )<br>(FSR_ADC B = $\pm V_{REF\_B}$ )                       | $V_{CM\_A} = \left\{ \frac{V_{REF\_A}}{2} \right\} \pm 0.1V$<br>$V_{CM\_B} = \left\{ \frac{V_{REF\_B}}{2} \right\} \pm 0.1V$ |     |

| INPUT_RANGE = 1<br>(FSR_ADC_A = $\pm 2 \times V_{REF\_A}$ )<br>(FSR_ADC_B = $\pm 2 \times V_{REF\_B}$ ) | $V_{CM\_A} = V_{REF\_A} \pm 0.1V$<br>$V_{CM\_B} = V_{REF\_B} \pm 0.1V$                                                       |     |

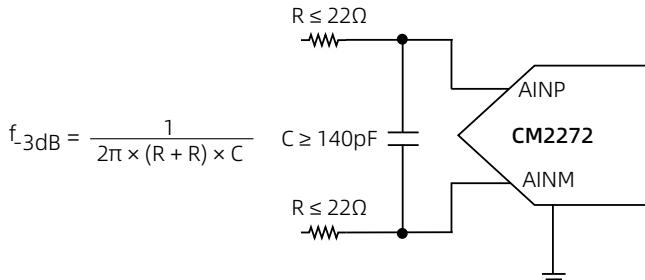

## 抗混叠滤波器

模数转换需以固定频率对输入信号采样。根据奈奎斯特采样定理，若输入信号中包含高于 1/2 采样频率的频率成分，这些高频信号会以混叠形式折叠到低频波段，造成失真。为避免混叠，必须在 ADC 采样前使用模拟抗混叠滤波器滤除输入信号中的高频谐波。典型的抗混叠滤波器采用 RC 低通结构，其截止频率需根据应用需求优化：

- 对于含快速瞬变的直流信号（如多路复用信号），需较高截止频率，以确保信号在 ADC 采样窗口内充分建立；

- 对于交流信号，则应限制带宽以抑制噪声，从而提高系统信噪比 SNR。

在 ADC 输入端并联的滤波电容 C 具有多重功能：可滤除前端电路噪声、抑制采样电荷注入，并为内部采样保持电容提供快速充电通路。根据工程经验，该电容值应至少为 ADC 采样电容的 10

倍。CM2272 采样电容为 14pF，因此 C 需大于 140pF。电容应选用 COG 或 NPO 型陶瓷材质，此类电容具有高 Q 值、低温漂特性，且在电压、频率及时效变化下仍保持稳定，可保障系统在不同工况下的测量精度。

需注意，驱动容性负载可能恶化放大器的相位裕度，影响系统稳定性。为避免该问题，通常在放大器输出端串联隔离电阻 R。增大 R 可提升稳定性（相位裕度改善约 10°~15°），但会因 ADC 非线性输入阻抗引入失真，失真程度随源阻抗、信号频率及幅度的增加而加剧。因此需权衡稳定性与失真度，选择合适的 R 值。

建议将 R 控制在 22Ω 以内，以保持线性度。电阻容差选用 1% 即可，差分输入端的匹配电容可补偿电阻失配带来的共模误差（实测增益误差 < 0.05%）。

图 17 抗混叠滤波器

图 18 抗混叠滤波器

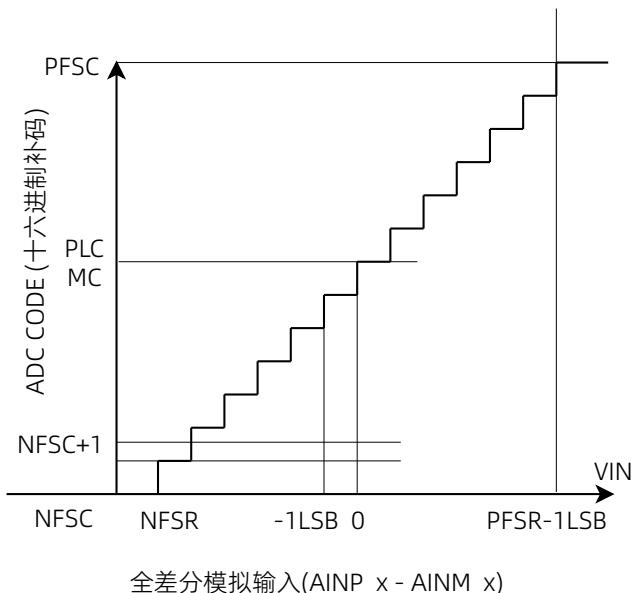

CM2272 的理想传递特性如图 19 所示。

图 19 理想传递函数

表 1 显示了不同输入电压和对应输出码之间的对应关系。

## ADC 传递函数

CM2272 的输出编码是全差分模拟输入范围的二进制补码。

全差分输入条件下的分辨率计算公式为：

$$1\text{LSB} = (2 \times \text{FSR\_ADC\_x}) / 2^N$$

其中， $N = 16$ ， $\text{FSR\_ADC\_x}$  为  $\text{ADC\_x}$  的满量程输入范围。

表 1 传递函数特性

| 输入电压( $\text{AINP}_x - \text{AINM}_x$ )， $\pm V_{\text{REF}}$ 范围 | 输入电压( $\text{AINP}_x - \text{AINM}_x$ )， $\pm 2 \times \pm V_{\text{REF}}$ 范围 | 输入电压           | 输出码值 (十六进制) |

|------------------------------------------------------------------|-------------------------------------------------------------------------------|----------------|-------------|

| $< -V_{\text{REF}}_x$                                            | $< -2 \times V_{\text{REF}}_x$                                                | NFSC           | 8000        |

| $-V_{\text{REF}}_x + 1\text{LSB}$                                | $-2 \times V_{\text{REF}}_x + 1\text{LSB}$                                    | NFSR           | 8001        |

| $-1\text{LSB}$                                                   | $-1\text{LSB}$                                                                | $-1\text{LSB}$ | FFFF        |

| 0                                                                | 0                                                                             | 0              | 0000        |

| $> V_{\text{REF}}_x - 1\text{LSB}$                               | $> 2 \times V_{\text{REF}}_x - 1\text{LSB}$                                   | PFSR - 1LSB    | 7FFF        |

## 数字接口

CM2272 通过串行接口进行通信，串行接口包含 $\overline{CS}$ 、SCLK、SDOA、SDOB 及 SDI 共五条信号。其中，片选信号 $\overline{CS}$ 作为串行通信的核心控制信号，主要用于界定串行数据传输的起始与结束，并触发 ADC 转换操作的启动。当 $\overline{CS}$ 信号产生下降沿时，ADC 完成对模拟输入信号的采样，同时数据总线从高阻态（三态）退出并进入有效数据传输状态。

SCLK 信号的主要功能是为 SDOA/SDOB 与 SDI 之间的数据输入/输出提供同步时钟基准。寄存器读写操作至少需要 16 个 SCLK 周期完成，而转换结果的读取所需最小 SCLK 周期数则取决于芯片当前工作模式。

CM2272 提供两路独立的串行输出通道 SDOA 和 SDOB，用户可通过配置 CONFIG 寄存器中的 RD\_DATA\_LINES 位，灵活选择单线或双线串行输出模式：

- 低采样率或过采样场景：可采用单线模式（仅使用 SDOA 信号）读取结果，简化接口设计并降低资源占用；

- 最大采样率场景：推荐使用双线模式读取转换结果，以充分利用并行输出能力，满足高速数据传输需求。

## 读取转换结果

CM2272 提供四种接口模式用于读取转换结果，可灵活适配不同硬件与固件。

需特别说明的是，CM2272 在 16-SCK 模式下，存在 1 个转换周期的读取延迟，因此转换完成后的结果需等待至下一次串行接口访问时方可被读取。在此过程中，当片选信号 $\overline{CS}$ 保持低电平时，转换结果将通过两路串行输出管脚(SDOA/SDOB)以 16 位（单线模式则为 32 位）串行数据流形式依次移出：其中 MSB 在 $\overline{CS}$ 下降沿后输出，后续各位数据则在 SCLK 的上升沿依次移位输出，输出数据在 SCLK 上升沿和下降沿均可采样，只需确保系统有足够的保持时间即可。当 16 位转换数据全部移出后，片选信号 $\overline{CS}$ 将拉高，此时两路串行输出管脚(SDOA/SDOB)自动切换至高阻态，释放总线资源。

表 2 接口模式选择

| RD_CLK_MODE | RD_DATA_LINES | 接口模式                     | 读取转换结果需要的最小时钟周期数 (N) |

|-------------|---------------|--------------------------|----------------------|

| 0           | 0             | 32-SCK 双线 SDO 输出模式（默认配置） | 32                   |

| 0           | 1             | 32-SCK 单线 SDO 输出模式       | 48                   |

| 1           | 0             | 16-SCK 双线 SDO 输出模式       | 16                   |

| 1           | 1             | 16-SCK 单线 SDO 输出模式       | 32                   |

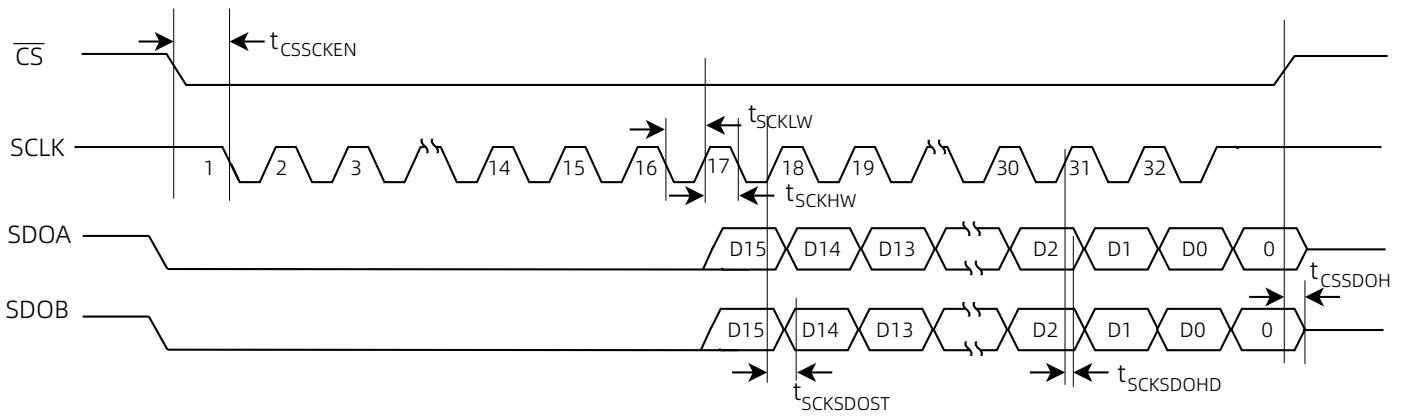

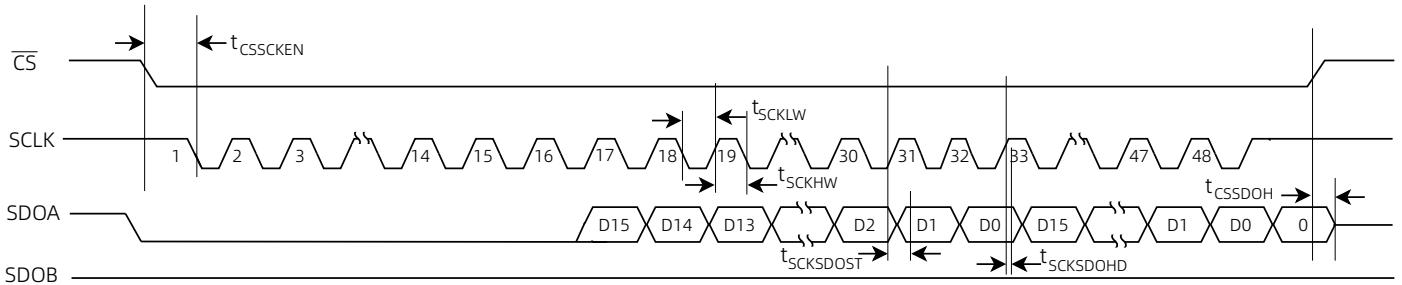

## 32-SCK SDO 输出模式

该模式可通过配置 RD\_CLK\_MODE = 0 启用。该模式下， $\overline{CS}$ 下降沿启动新的一次转换。其数据流输出逻辑为： $\overline{CS}$ 下降沿后，SDO 总线由高阻态变为输出固定值 0。随后从第 16 个 SCLK 上升沿开始将 MSB 位数据依次移出。数据输出完成后， $\overline{CS}$ 由低电平变为高电平，SDO 再次恢复为高阻态。需注意的是，32-SCK 模式下，数据输出为当次转换的结果，没有延时。

[图 20](#) 和 [图 21](#) 详细展示了该模式的时序规范。

图 20 32-SCK 双线 SDO 接口时序

图 21 32-SCK 单线 SDO 接口时序

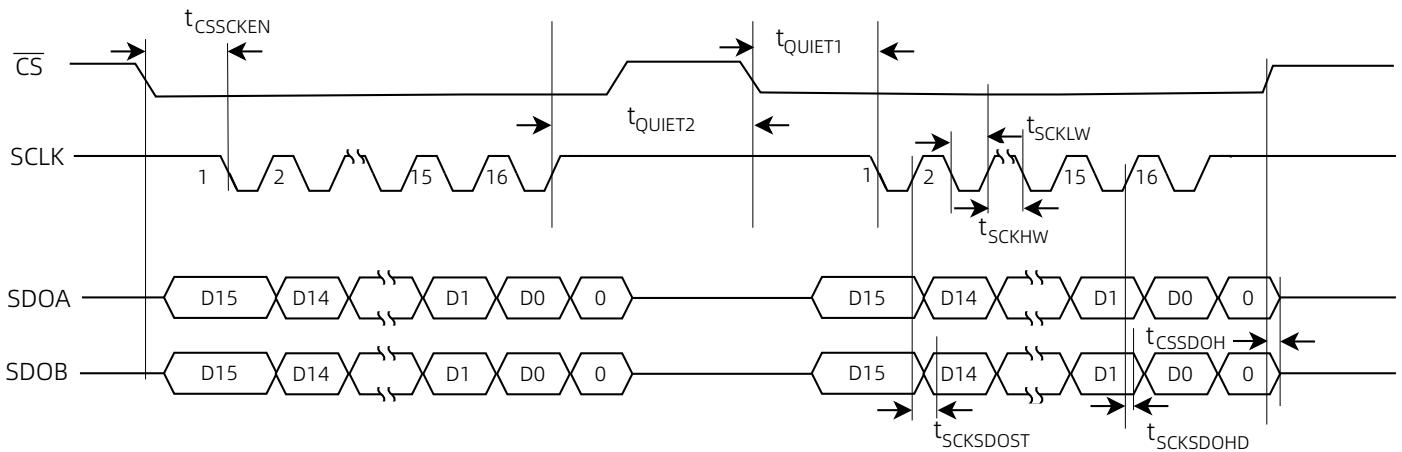

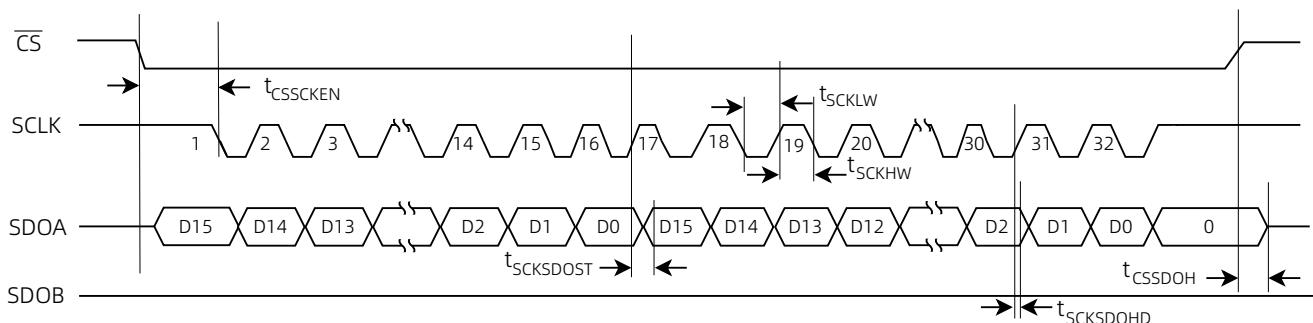

## 16-SCK SDO 输出模式

该模式可通过配置 RD\_CLK\_MODE = 1 启用。该模式下， $\overline{CS}$ 下降沿启动新的一次转换。其数据流输出逻辑为： $\overline{CS}$ 下降沿后，SDO 总线由高阻态变为输出转换结果的 MSB。随后的 SCLK 上升沿将 MSB - 1 位到第 0 位数据依次移出。数据输出完成后， $\overline{CS}$ 由低电平变为高电平，SDO 再次恢复为高阻态。需注意的是，16-SCK 模式下，数据输出有一个转换周期的延时，即数据输出上一次的转换结果。转换期间，SCLK 上的数字活动对 SAR ADC 会造成干扰。为了获得最佳的 ADC 性能，建议发送 SCLK 时，满足  $t_{QUIET1}$  和  $t_{QUIET2}$  的时序要求。

[图 22](#) 和 [图 23](#) 详细展示了该模式的时序规范。

图 22 16-SCK 双线 SDO 输出模式

图 23 16-SCK 单线 SDO 输出模式

## 读寄存器数据

CM2272 内置两个可通过串行接口读取的寄存器：CONFIG 配置寄存器和 DEVICE\_ID 设备标识寄存器。执行读取操作时，主机首先发送一个 16 位读命令帧。芯片在接收读命令帧的同时，SDOA/SDOB 将根据之前的配置通过 SCLK 上升沿移出对应数据，如图 24 所示。芯片接收并解析到读命令后，主机随后发送一个空命令帧（保持 SDI = 0，只发送 16 个 SCLK），芯片将在此时通过 SDOA 管脚逐位输出所选寄存器的内容，SDOB 保持为低电平。读命令帧格式如表 3 所示。

图 24 串行读取操作

表 3 读命令帧格式

| 寄存器       | [D15:D12] | [D11:D0] |

|-----------|-----------|----------|

| CONFIG    | 0011      | 0000     |

| DEVICE_ID | 0100      | 0000     |

## 写寄存器数据

CM2272 提供单一配置寄存器 CONFIG，用户可通过写命令配置该寄存器，实现工作模式的灵活配置，包括：

- 数据输出模式（单线/双线）

- 时钟周期模式 (16-SCK/32-SCK)

当前写命令帧包含的配置信息，将在下一次转换周期生效。发送写命令帧同时，SDOA/SDOB 将根据之前的配置通过 SCLK 上升沿移出对应数据，如图 25 所示。写命令帧格式如表 4 所示。

图 25 串行写入操作

表 4 写命令帧格式

| 寄存器    | [D15:D12] | [D11:D0]              |

|--------|-----------|-----------------------|

| CONFIG | 0000      | 对应寄存器 D11:D0 位, 参见表 5 |

## 寄存器

CM2272 集成两个片内寄存器：CONFIG 寄存器（可读写）和 DEVICE ID 寄存器（只读）。参见[表 5](#) 和 [表 6](#)。

### 配置寄存器 (CONFIG)

CM2272 的 CONFIG 寄存器支持对芯片各种模式的灵活配置。需注意，其配置内容将在当前写操作完成后的下一次转换启动时生效。各配置位的具体功能定义如[表 5](#) 所示。

表 5 CONFIG

| 位     | 名称            | 访问类型 | 复位   | 描述                                                                                                 |

|-------|---------------|------|------|----------------------------------------------------------------------------------------------------|

| 15:12 | RESERVED      | R    | 0000 | 保留位                                                                                                |

| 11    | RD_CLK_MODE   | R/W  | 0    | 0: 32-SCK 模式<br>1: 16-SCK 模式                                                                       |

| 10    | RD_DATA_LINES | R/W  | 0    | 0: 双线输出，ADC_A 通道结果在 SDO_A 输出，ADC_B 通道结果在 SDO_B 输出<br>1: 单线输出，ADC_A 通道结果先在 SDO_A 输出，然后 ADC_B 通道结果输出 |

| 9     | INPUT_RANGE   | R/W  | 0    | 0: VREF<br>1: 2VREF                                                                                |

| 8:0   | RESERVED      | R    | 0    | 保留位                                                                                                |

### DEVICE ID 寄存器

DEVICE ID 寄存器为只读寄存器，用于存储芯片的唯一设备标识符，主机可通过读取该寄存器获取设备 ID。各配置位的具体功能定义如[表 6](#) 所示。

表 6 DEVICE ID

| 位     | 名称        | 访问类型 | 复位             | 描述    |

|-------|-----------|------|----------------|-------|

| 15:12 | RESERVED  | R    | 0000           | 保留位   |

| 11:0  | DEVICE_ID | R    | 0000 0010 0101 | 芯片 ID |

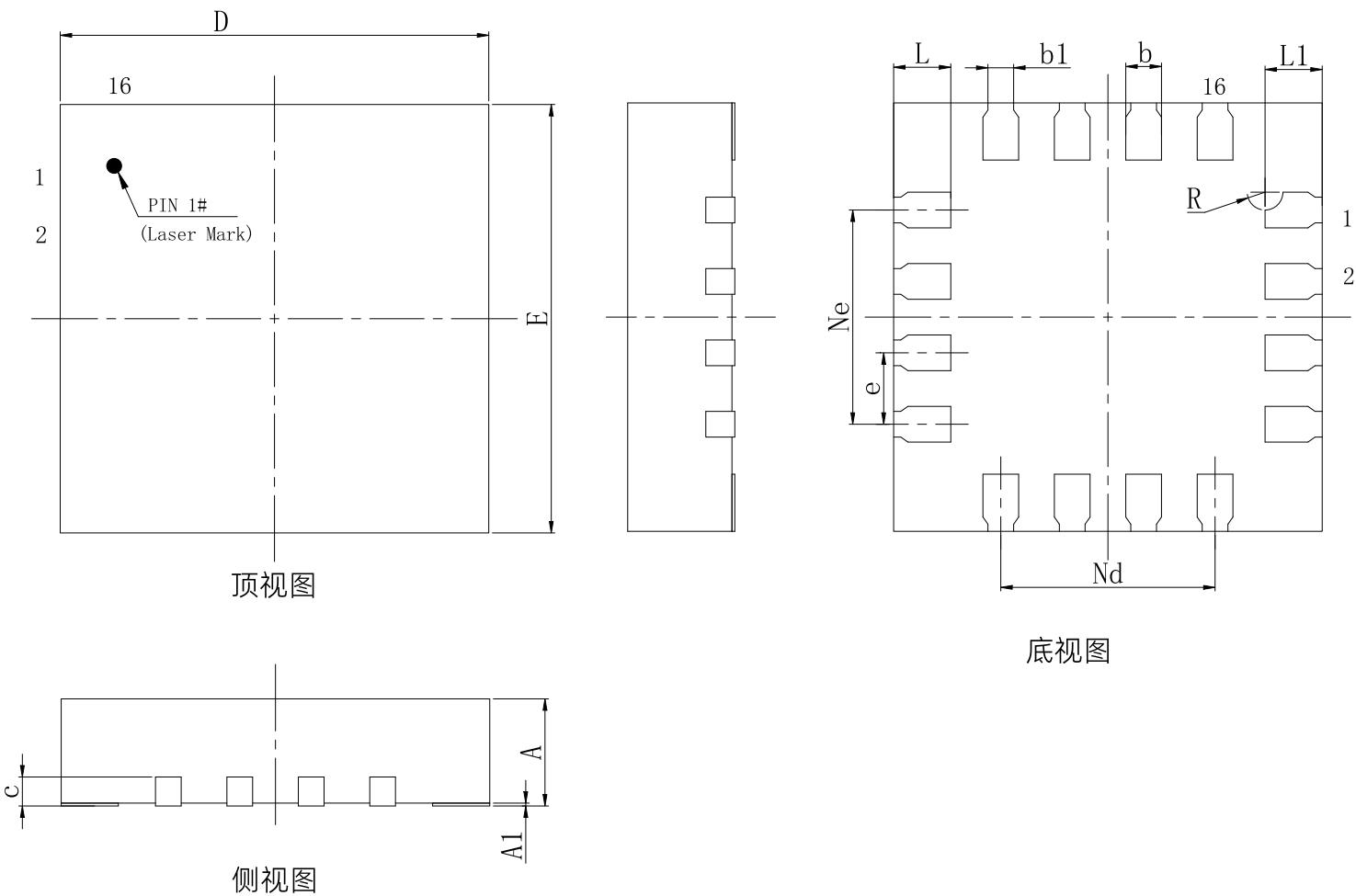

## 封装及订购信息

### 封装方式

CM2272 采用 QFN16 封装。

### 产品外形图

产品外形图如下图所示。

| 标识 | 尺寸 (毫米)    |      |      |

|----|------------|------|------|

|    | 最小值        | 典型值  | 最大值  |

| A  | 0.70       | 0.75 | 0.80 |

| A1 | 0          | 0.02 | 0.05 |

| b  | 0.20       | 0.25 | 0.30 |

| b1 | 0.18 (REF) |      |      |

| c  | 0.20 (REF) |      |      |

| D  | 2.90       | 3.00 | 3.10 |

| e  | 0.50 (BSC) |      |      |

| E  | 2.90       | 3.00 | 3.10 |

| Nd | 1.50 (BSC) |      |      |

| Ne | 1.50 (BSC) |      |      |

| L  | 0.35       | 0.40 | 0.45 |

| L1 | 0.30       | 0.40 | 0.50 |

| R  | 0.13 (REF) |      |      |

## 订购信息

| 型号           | 温度范围        | 封装    | 包装   | 包装数量 |

|--------------|-------------|-------|------|------|

| CM2272-QFNTR | -40°C~125°C | QFN16 | Reel | 5000 |